Table of Contents

Digitaltechnik Praktikum - Tutorial Simulation mit Modelsim

In diesem Tutorial lernen Sie den Schaltungssimulator Modelsim kennen. Als Beispiel wird die ledsw Schaltung aus Digitaltechnik Praktikum - Einführung Quartus verwendet.

Simulation mit Modelsim - Manuelles Aufsetzen des Projektes

Ähnlich wie bei der Software Quartus gibt es auch bei dem Simulator einen Assistenten um ein Projekt aufzusetzen. Wechseln Sie dazu in das Verzeichnis “digitaltechnikpraktikum/sim/ledsw”.

cd cd digitaltechnikpraktikum cd sim cd ledsw

In diesem Verzeichnis befinden sich schon zwei Dateien, die allerdings erst später bei der make basierten Umgebung verwendet werden. Für die Simulation der Schaltung werden zwei VHDL benötigt:

die sich beide im src Verzeichnis des Projektes befinden. Starten Sie jetzt die Modelsim Simulationssoftware im Verzeichnis “sim/ledsw”.

vsim

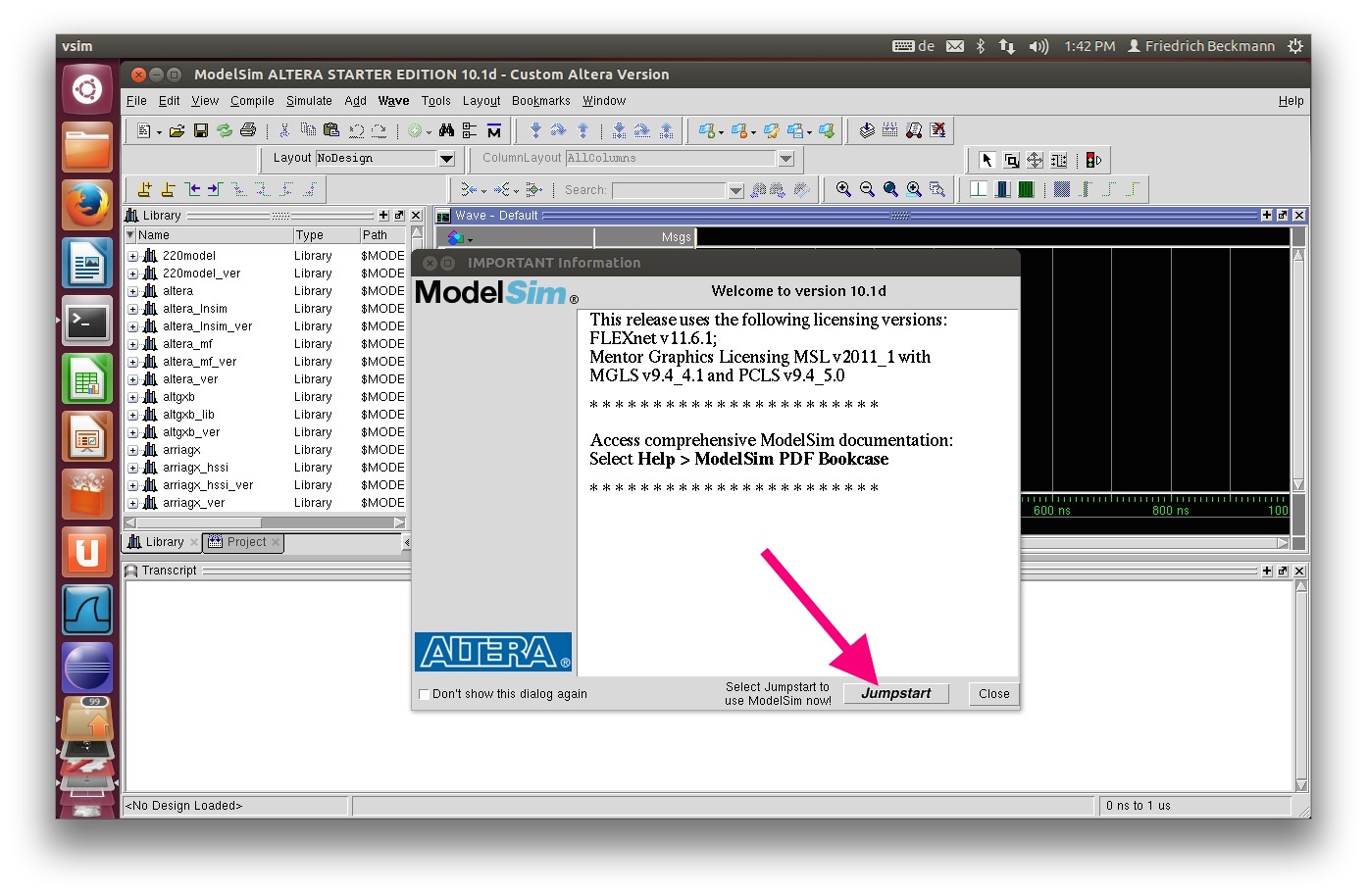

Drücken Sie “Jumpstart”

Drücken Sie “Jumpstart”

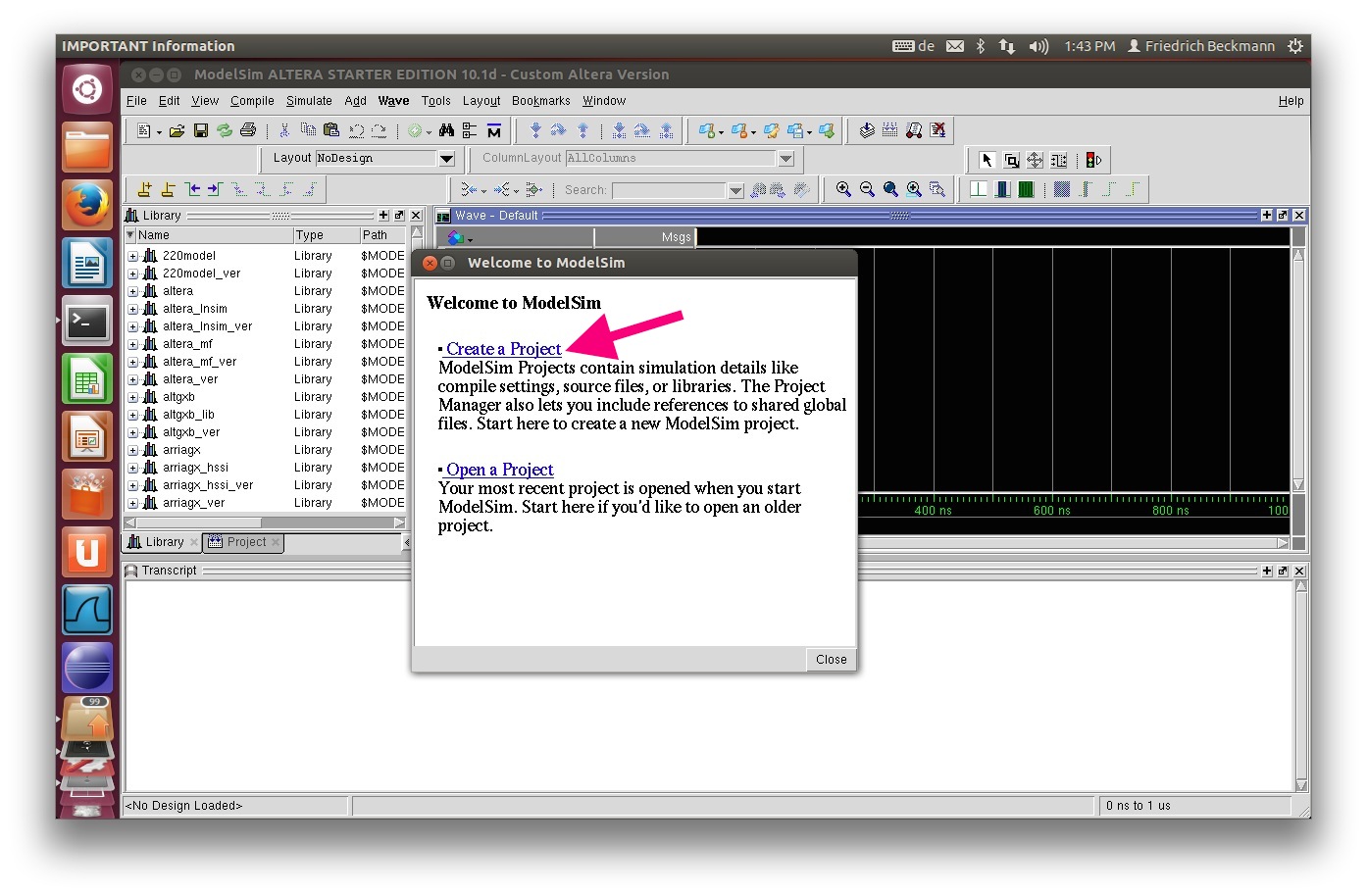

und dann “Create Project”.

und dann “Create Project”.

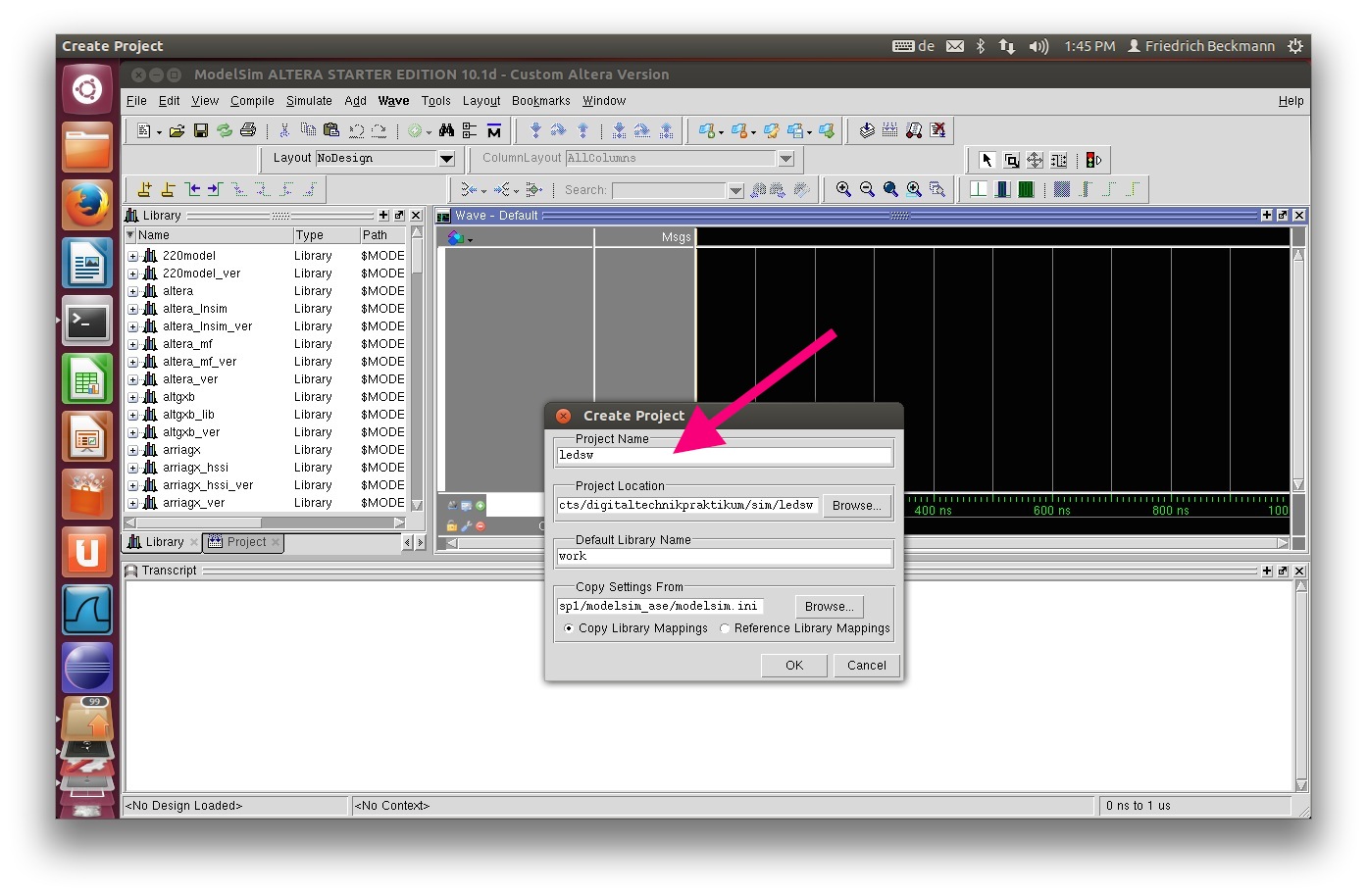

Geben Sie als Projektnamen “ledsw” ein.

Geben Sie als Projektnamen “ledsw” ein.

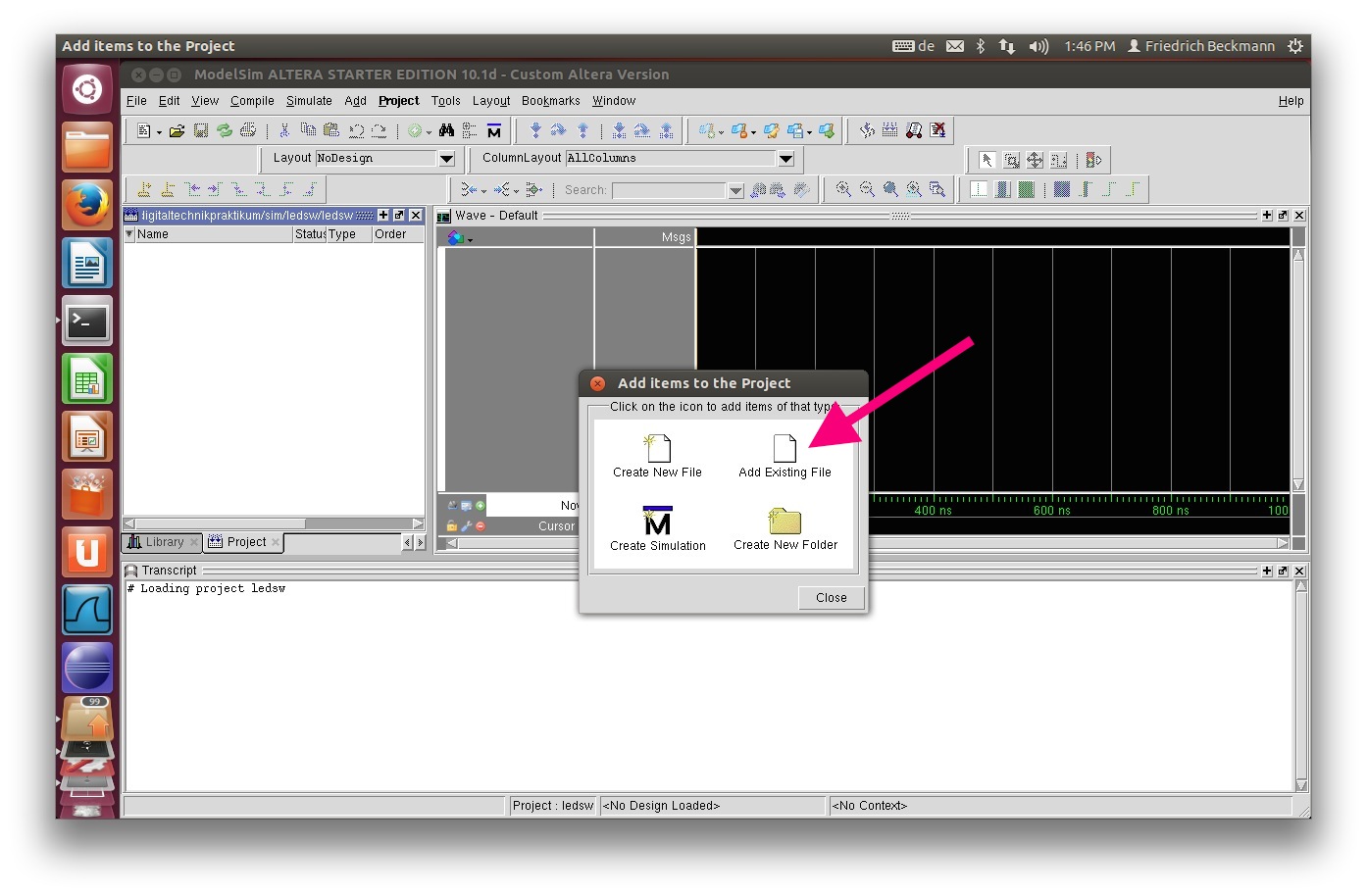

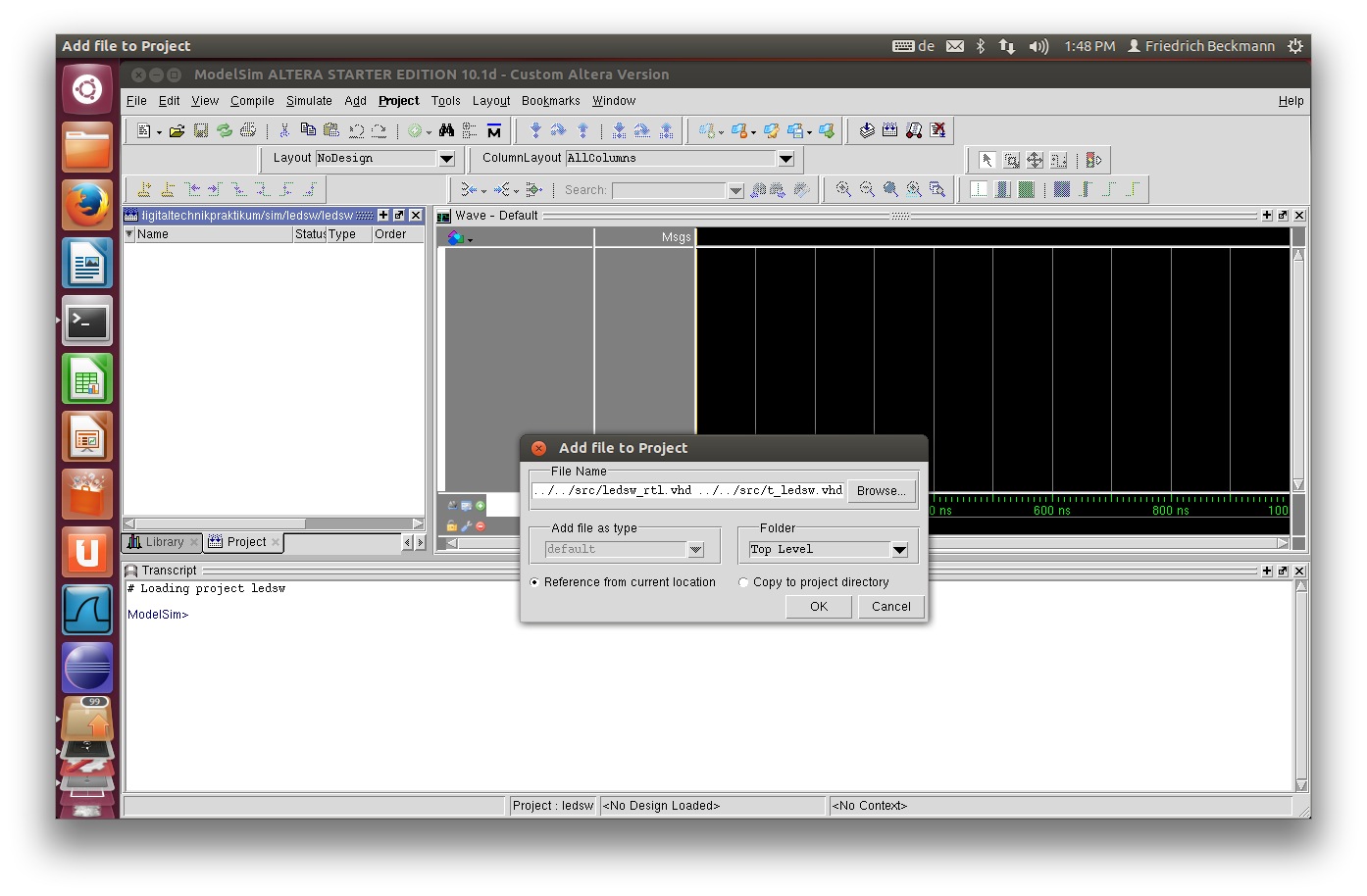

Fügen Sie die beiden VHDL Dateien zum Projekt hinzu.

Fügen Sie die beiden VHDL Dateien zum Projekt hinzu.

Geben Sie dazu die Dateien mit den relativen Pfaden an. Also

Geben Sie dazu die Dateien mit den relativen Pfaden an. Also

- ../../src/ledsw_rtl.vhd und

- ../../src/t_ledsw.vhd

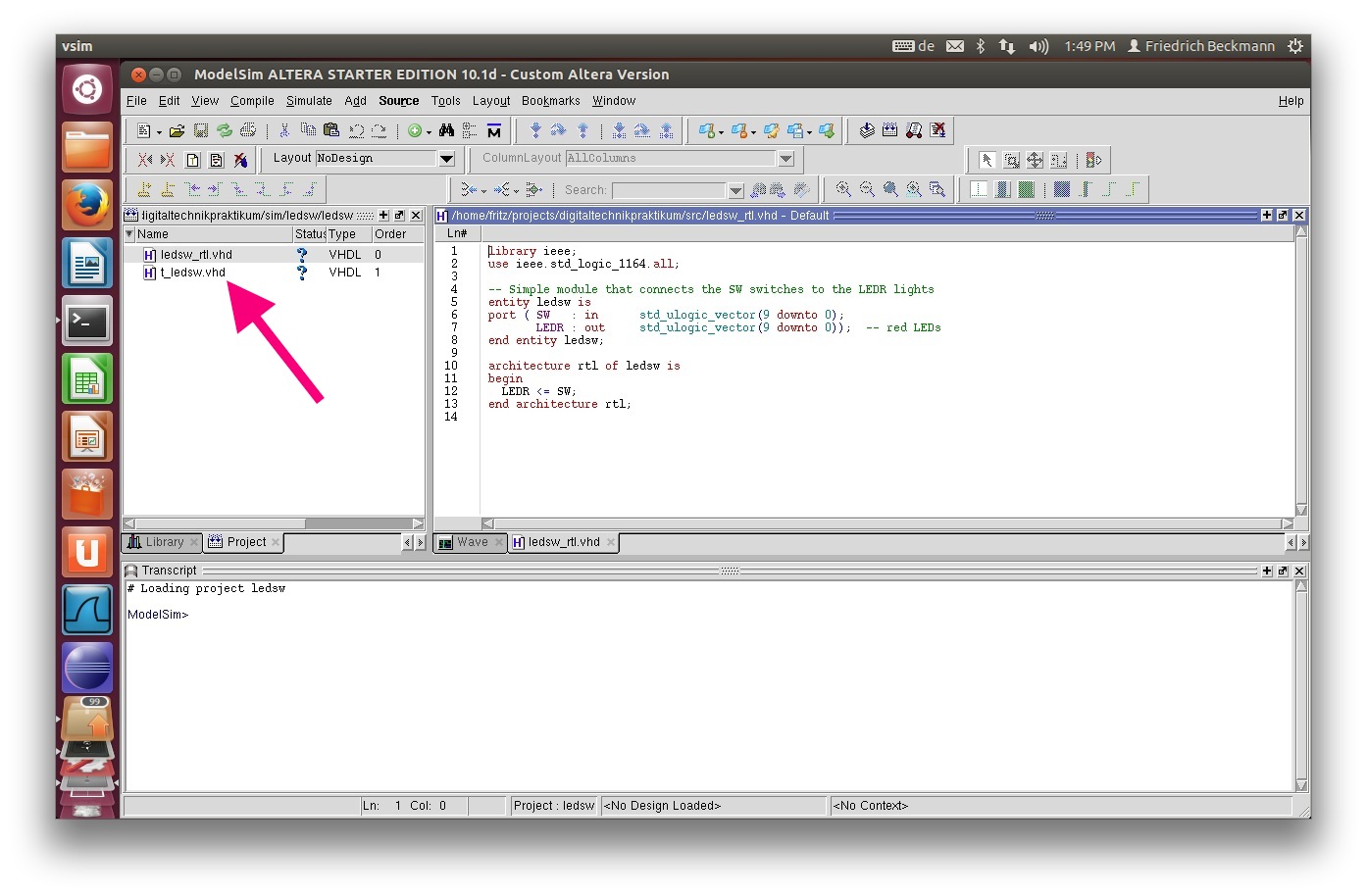

Danach erscheinen die beiden VHDL Dateien im Projektfenster.

Danach erscheinen die beiden VHDL Dateien im Projektfenster.

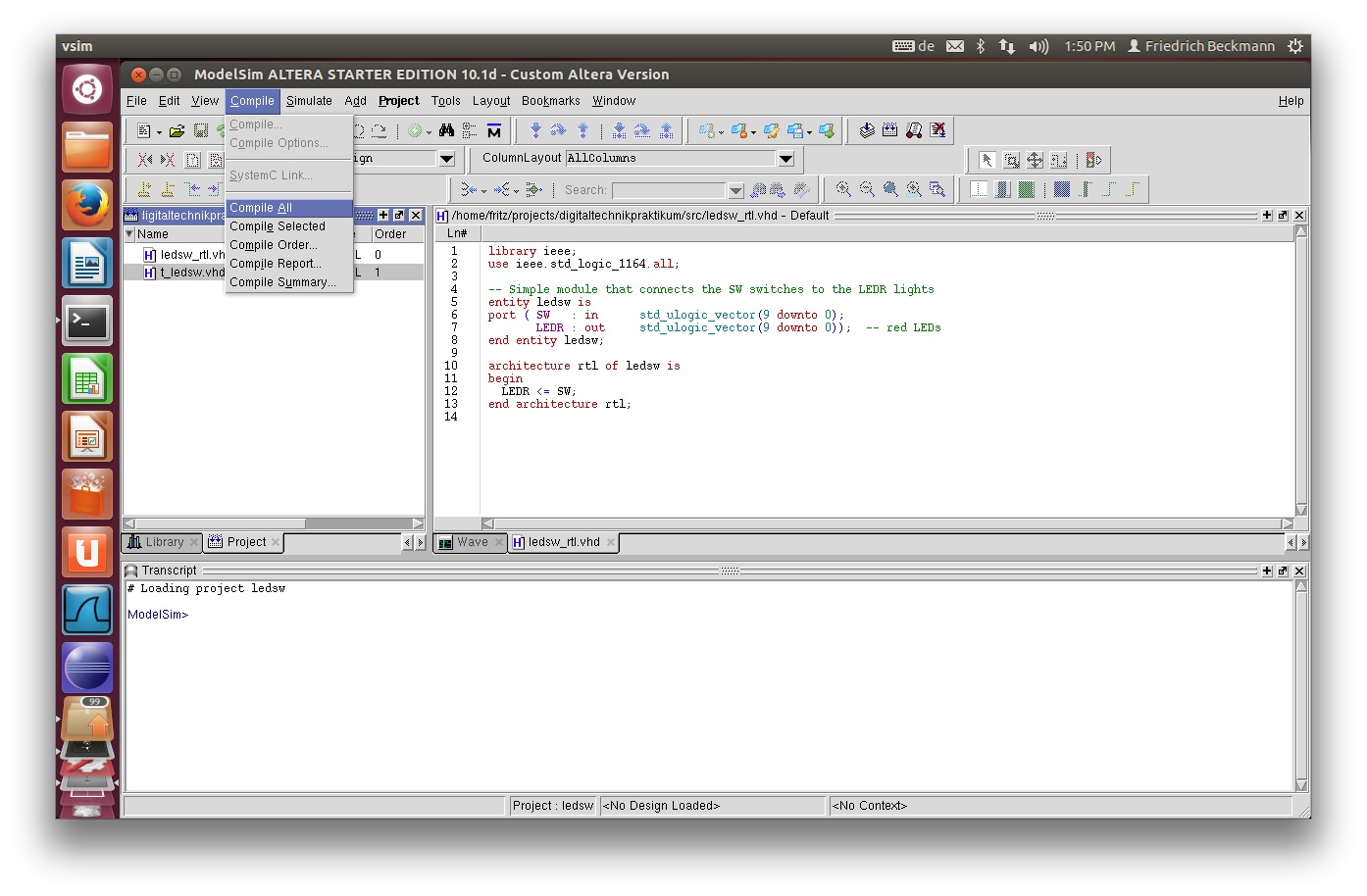

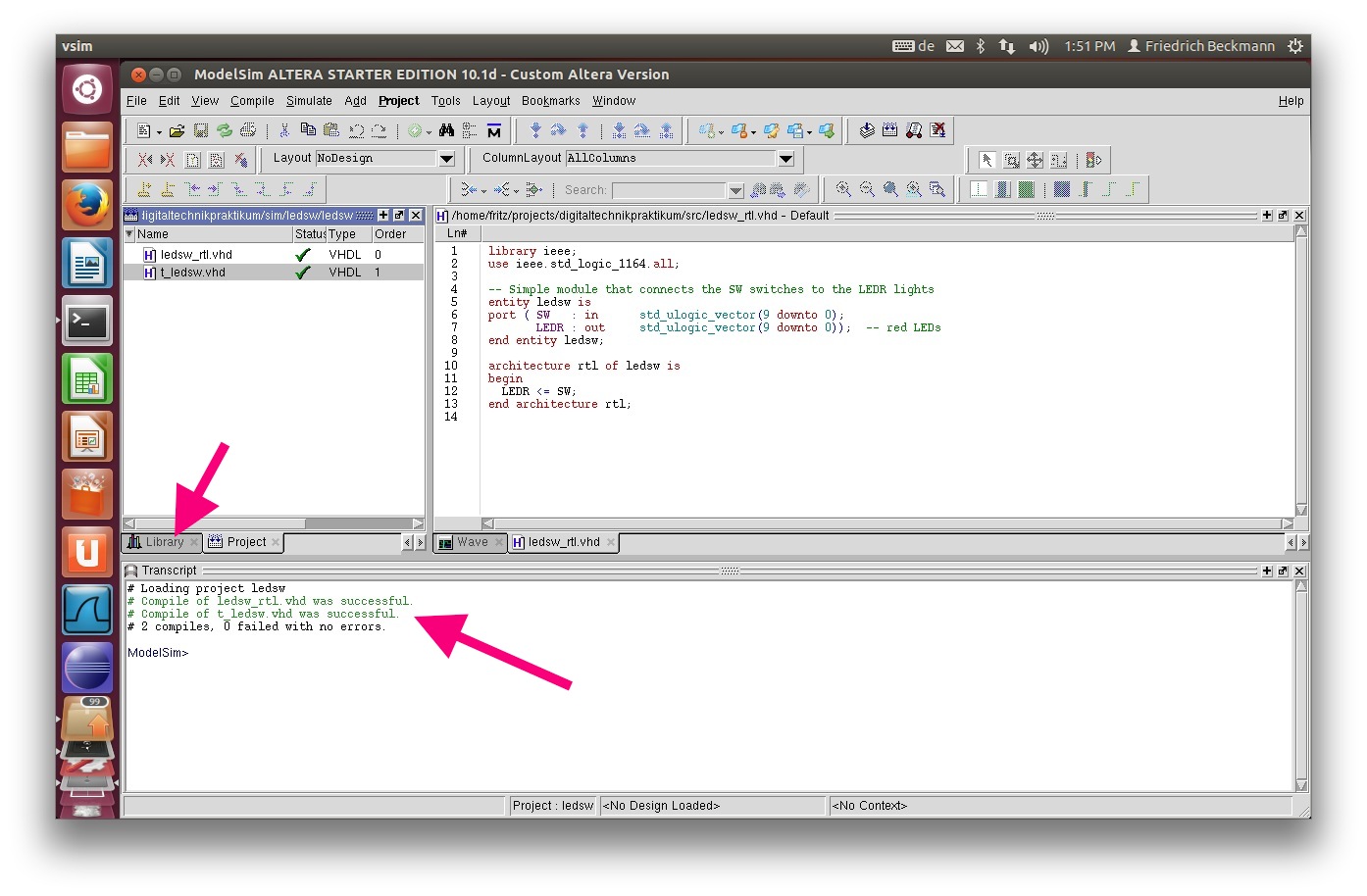

Die VHDL Dateien müssen für die Simulation zunächst übersetzt werden. Starten Sie Übersetzung mit “Compile → Compile All”.

Die VHDL Dateien müssen für die Simulation zunächst übersetzt werden. Starten Sie Übersetzung mit “Compile → Compile All”.

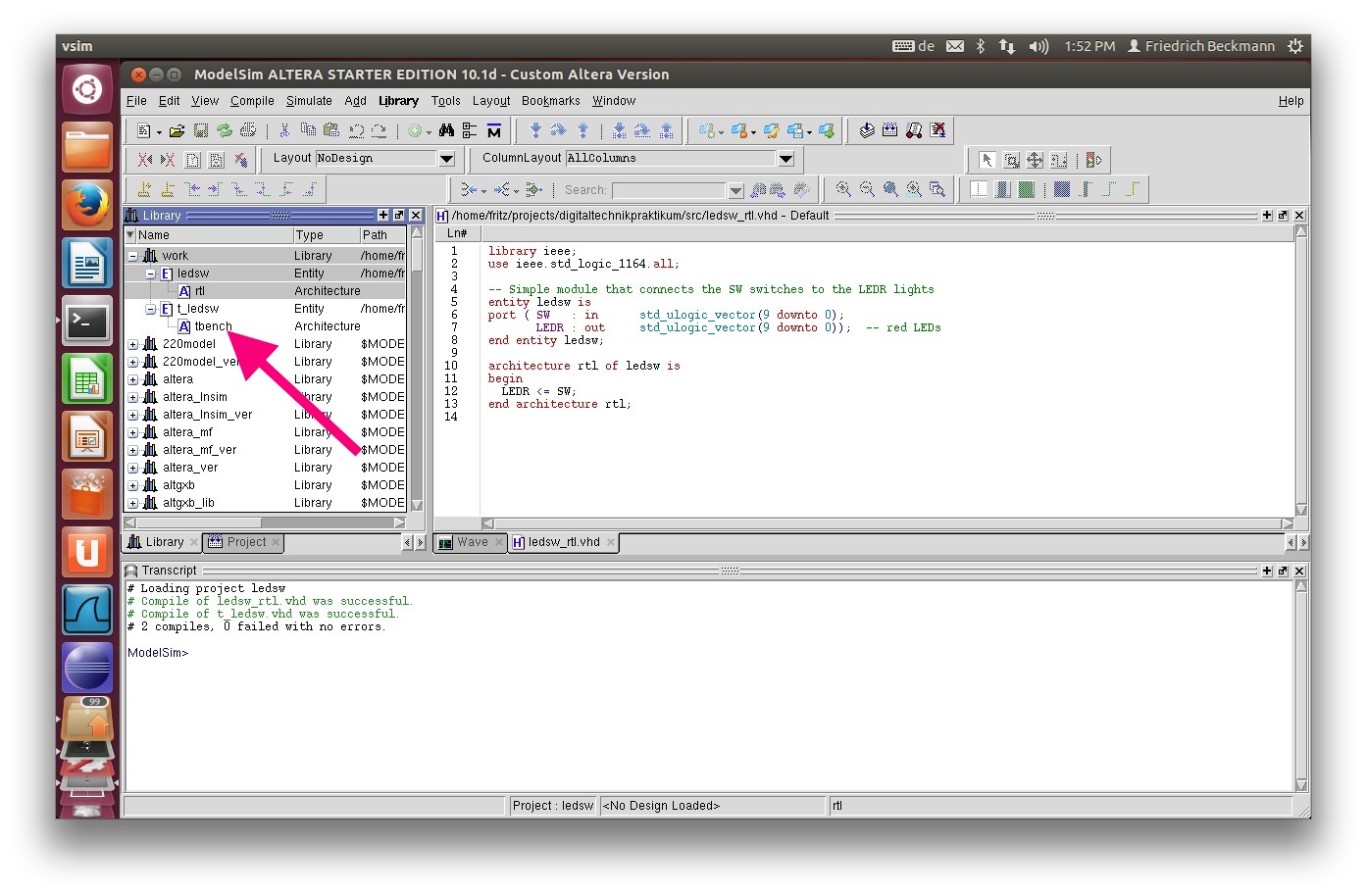

Wechseln Sie dann in Ansicht der Library. Dort wird das Ergebnis der Übersetzung der VHDL Quelldateien dargestellt.

Wechseln Sie dann in Ansicht der Library. Dort wird das Ergebnis der Übersetzung der VHDL Quelldateien dargestellt.

Zum Start der Simulation müssen Sie auf t_ledsw / tbench Architecture Doppelklicken. Dann wird der Simulator gestartet und die Daten aus der Library werden geladen. Die Simulation ist noch nicht gestartet.

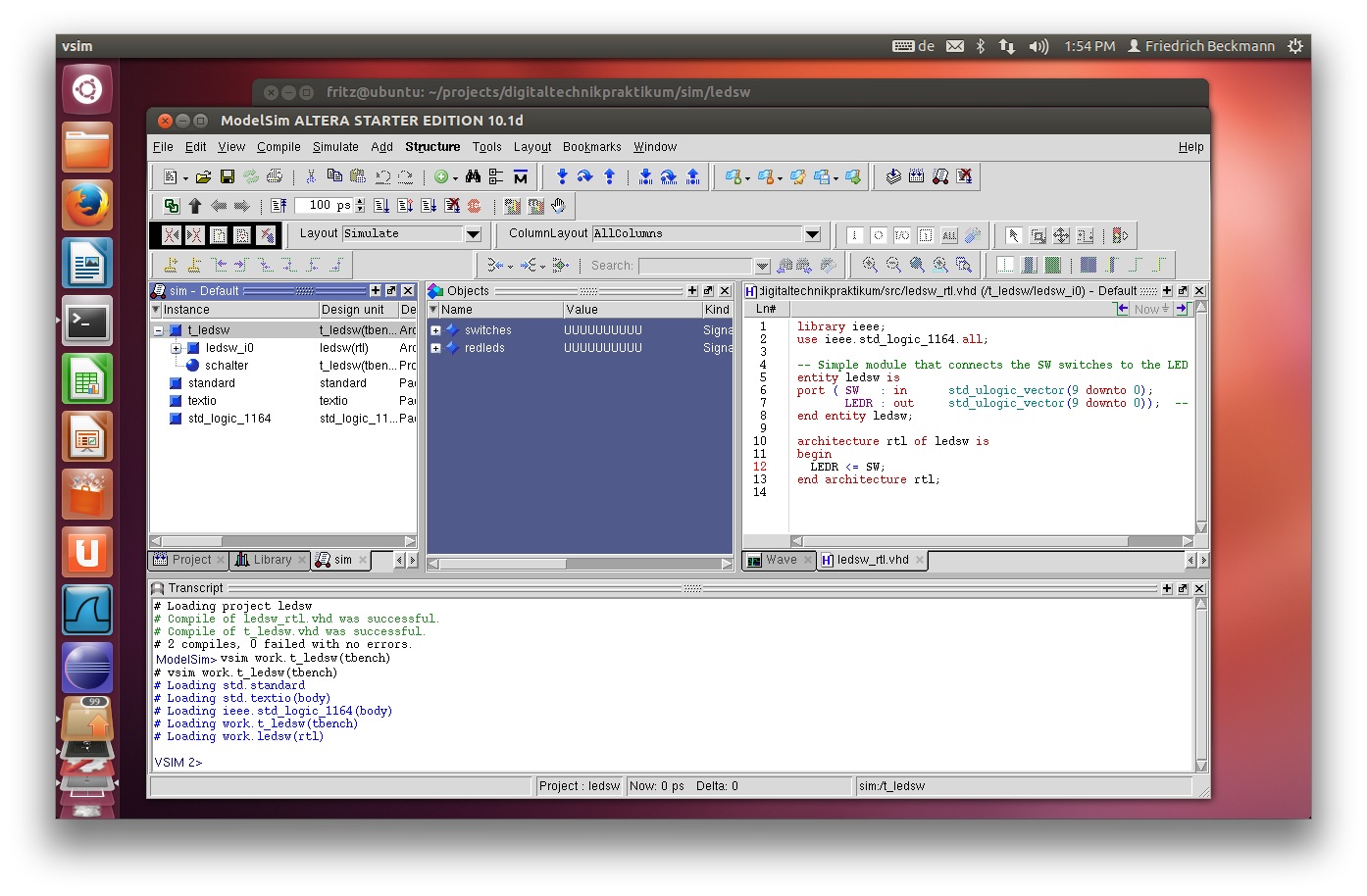

Links in der Simulatoransicht können Sie die Designhierarchie anschauen. Bei diesem einfachen Design ist der toplevel die Testbench “t_ledsw”, in der das Design “ledsw_i0” instantiiert ist. Um nach der Simulation auch den Signalverlauf von Signalen im Design beobachten zu können, müssen Sie die Signale zum Aufzeichnen auswählen.

Links in der Simulatoransicht können Sie die Designhierarchie anschauen. Bei diesem einfachen Design ist der toplevel die Testbench “t_ledsw”, in der das Design “ledsw_i0” instantiiert ist. Um nach der Simulation auch den Signalverlauf von Signalen im Design beobachten zu können, müssen Sie die Signale zum Aufzeichnen auswählen.

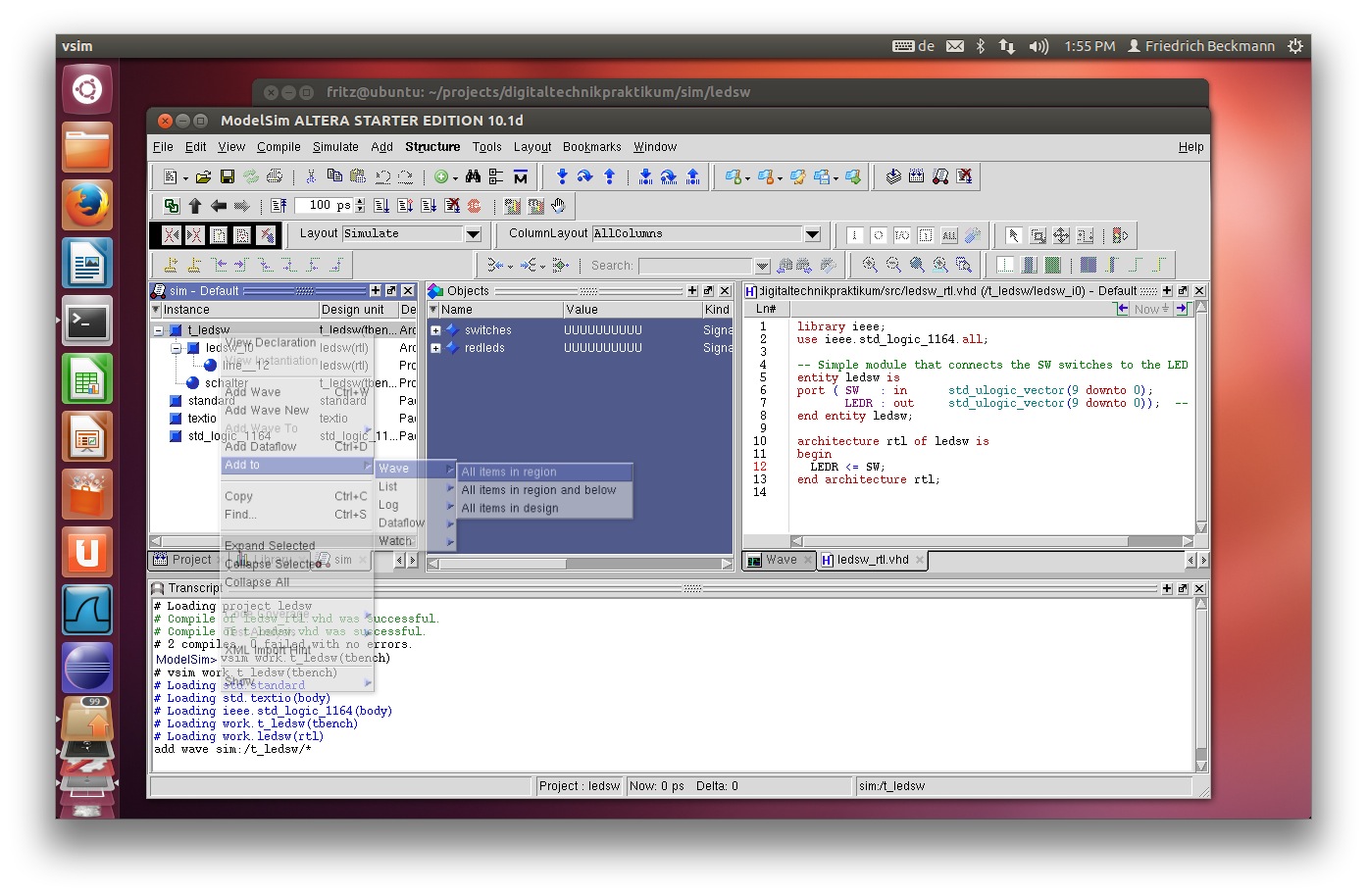

Wählen Sie dazu in der Simulatoransicht mit der rechten Maustaste das Kontextmenü bei “t_ledsw” und wählen Sie “Add to → Wave → All items in region”. Damit werden alle Signale in der Testbench “t_ledsw”, also die beiden Signale “switches” und “redleds” in das Waveform Fenster übernommen.

Wählen Sie dazu in der Simulatoransicht mit der rechten Maustaste das Kontextmenü bei “t_ledsw” und wählen Sie “Add to → Wave → All items in region”. Damit werden alle Signale in der Testbench “t_ledsw”, also die beiden Signale “switches” und “redleds” in das Waveform Fenster übernommen.

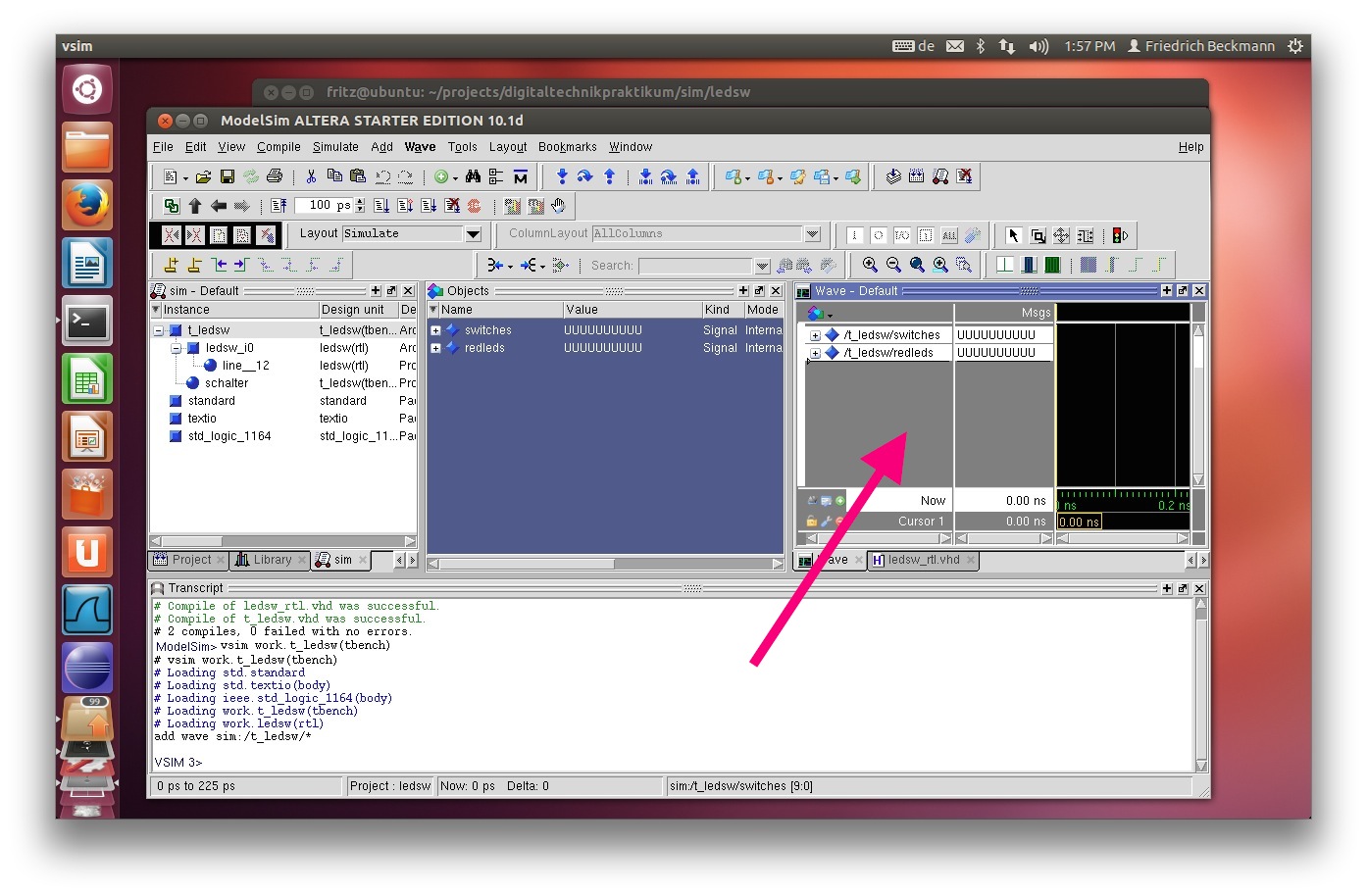

Wenn Sie das Waveform Fenster anklicken sehen Sie die beiden Signale.

Wenn Sie das Waveform Fenster anklicken sehen Sie die beiden Signale.

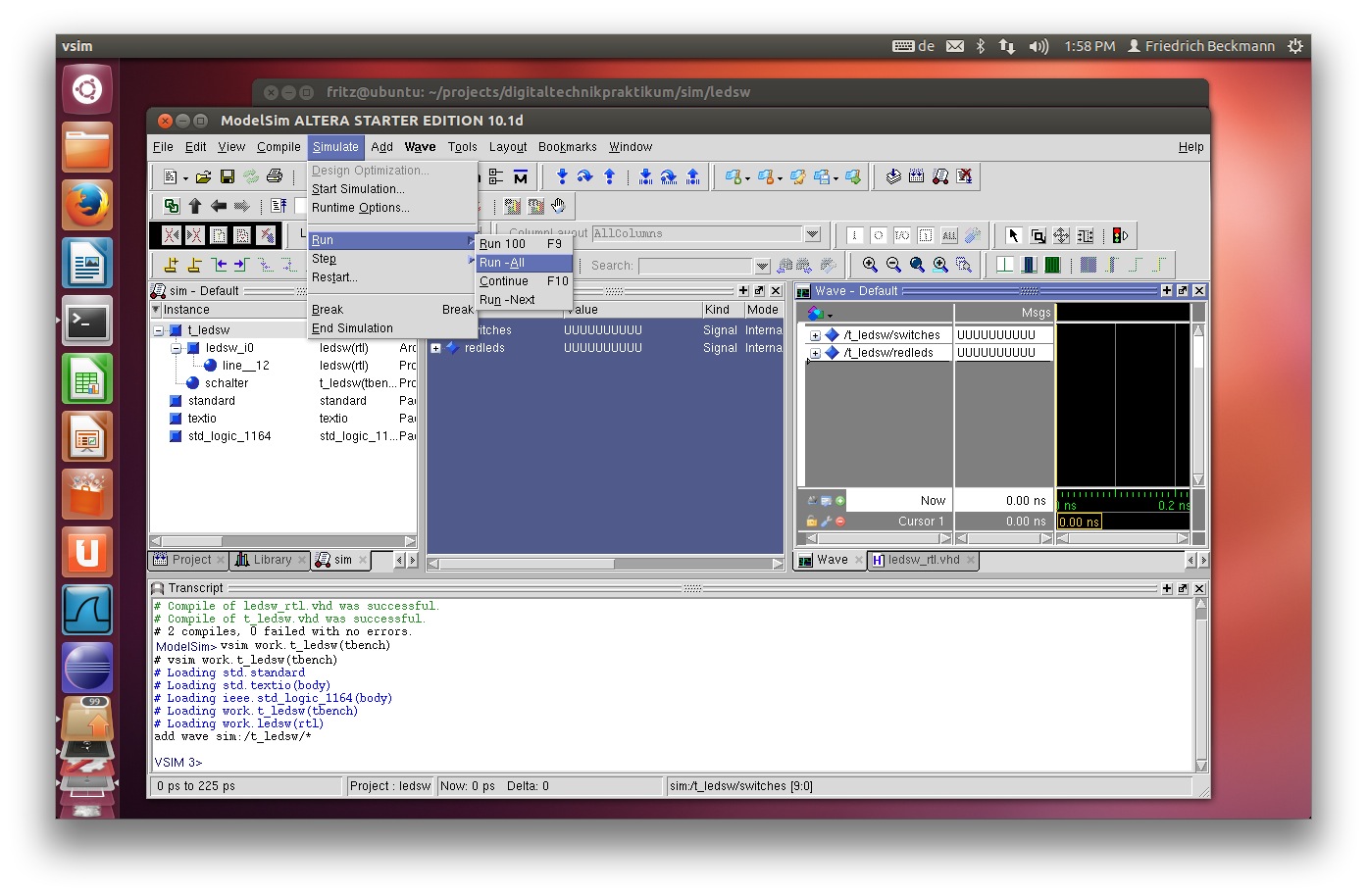

Jetzt starten Sie die Simulation mit “Simulate → Run → Run -all”.

Jetzt starten Sie die Simulation mit “Simulate → Run → Run -all”.

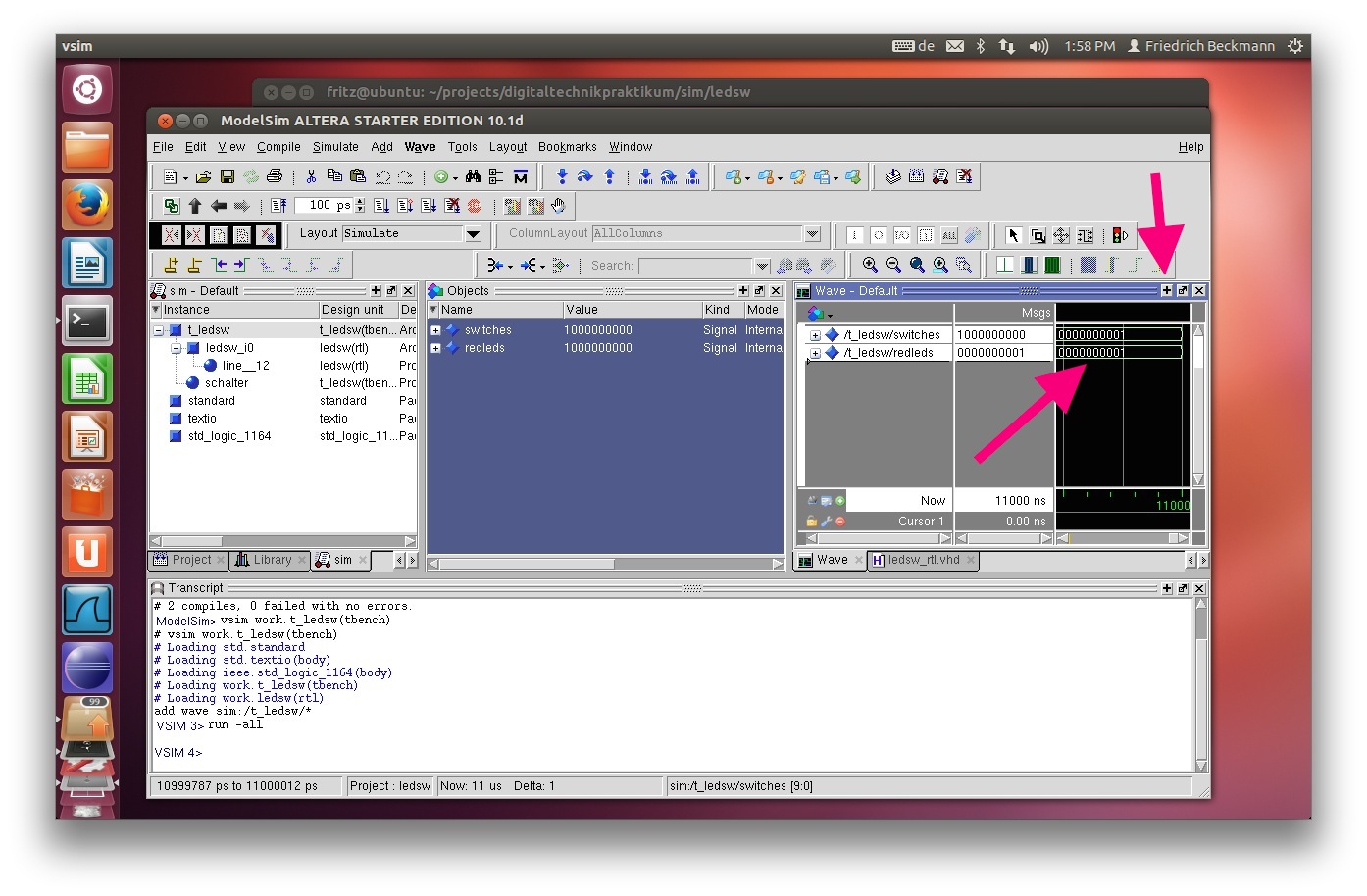

Um das Simulationsergebnis im Waveform Fenster anzuschauen, können Sie das Fenster durch drücken auf den “+” Knopf größer machen.

Um das Simulationsergebnis im Waveform Fenster anzuschauen, können Sie das Fenster durch drücken auf den “+” Knopf größer machen.

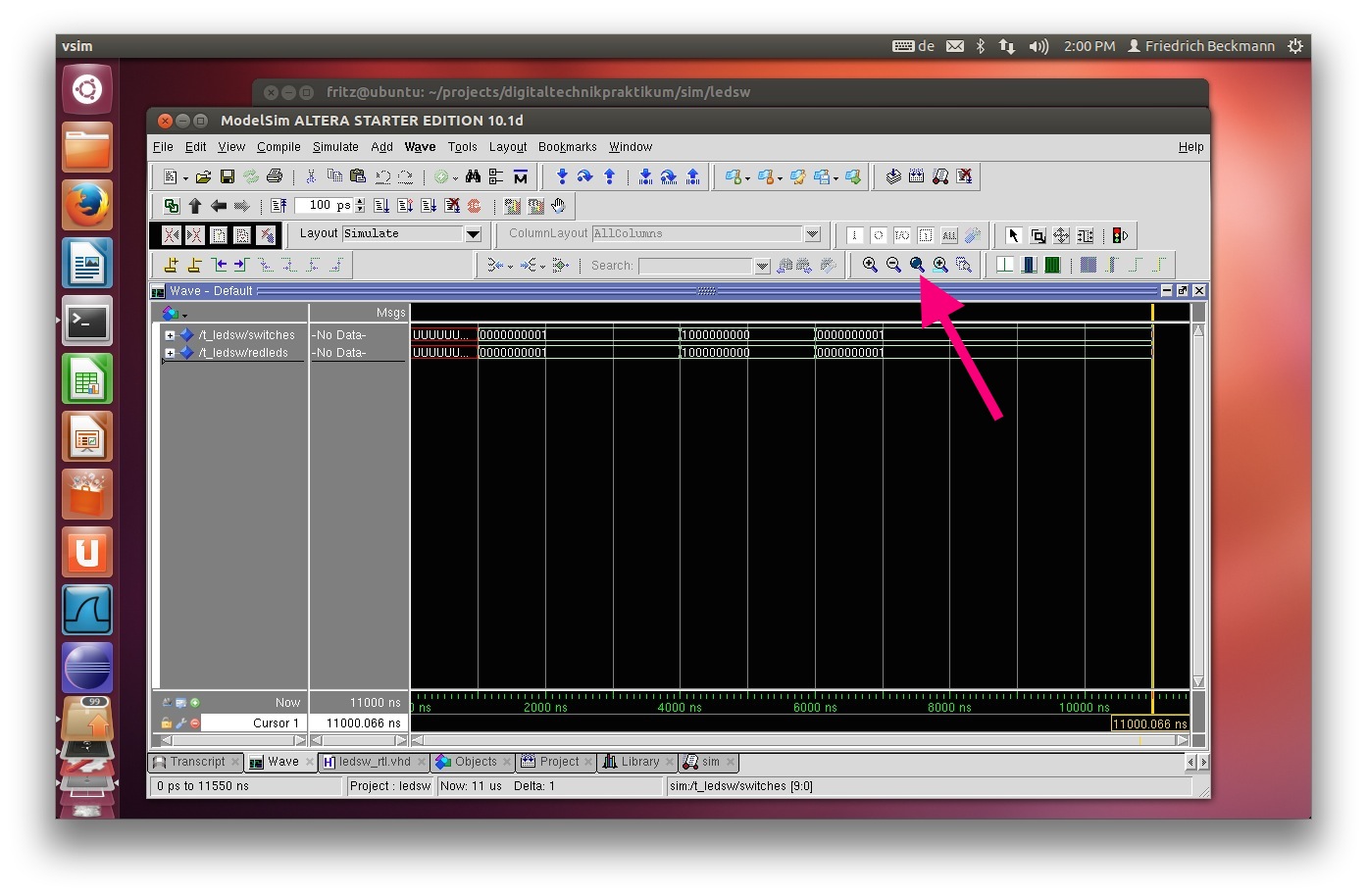

Um den gesamten Verlauf der Signale zu sehen drücken Sie auf den Knopf mit der Lupe (siehe Pfeil), oder wählen das Menü “Wave → Zoom → Zoom Full”. Sie können im Waveformfenster auch einfach die Taste “F” auf der Tastatur drücken.

Um den gesamten Verlauf der Signale zu sehen drücken Sie auf den Knopf mit der Lupe (siehe Pfeil), oder wählen das Menü “Wave → Zoom → Zoom Full”. Sie können im Waveformfenster auch einfach die Taste “F” auf der Tastatur drücken.

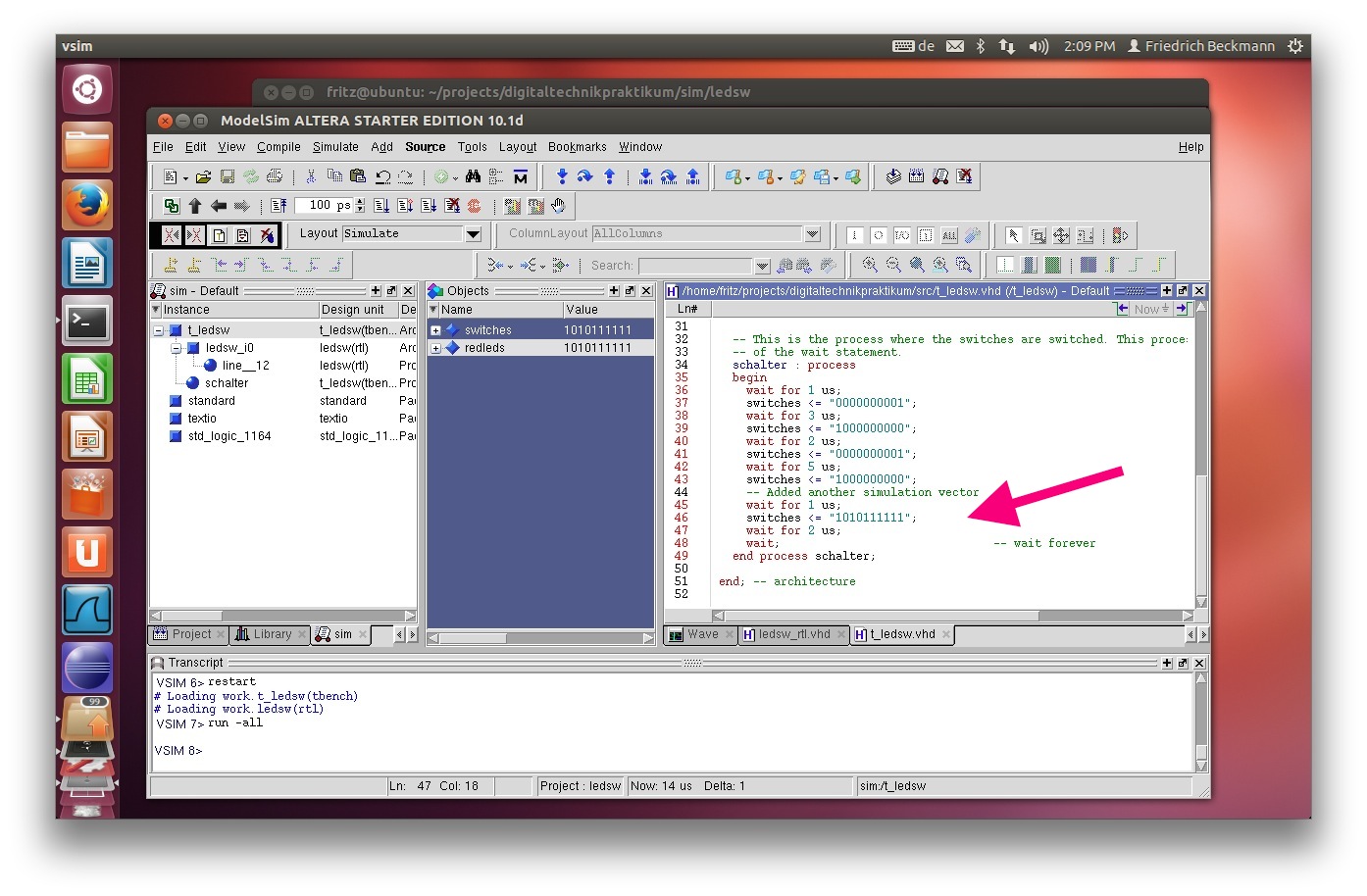

Jetzt haben Sie das Simulationsergebnis angeschaut. Im folgenden wird erläutert wie Sie vorgehen müssen um den Inhalt von VHDL Dateien zu ändern und die Simulation neu zu starten. Dazu wird hier als Beispiel ein neuer Simulationsvektor “1010111111” ergänzt. Dazu muss die Datei “t_ledsw.vhd” geändert werden.

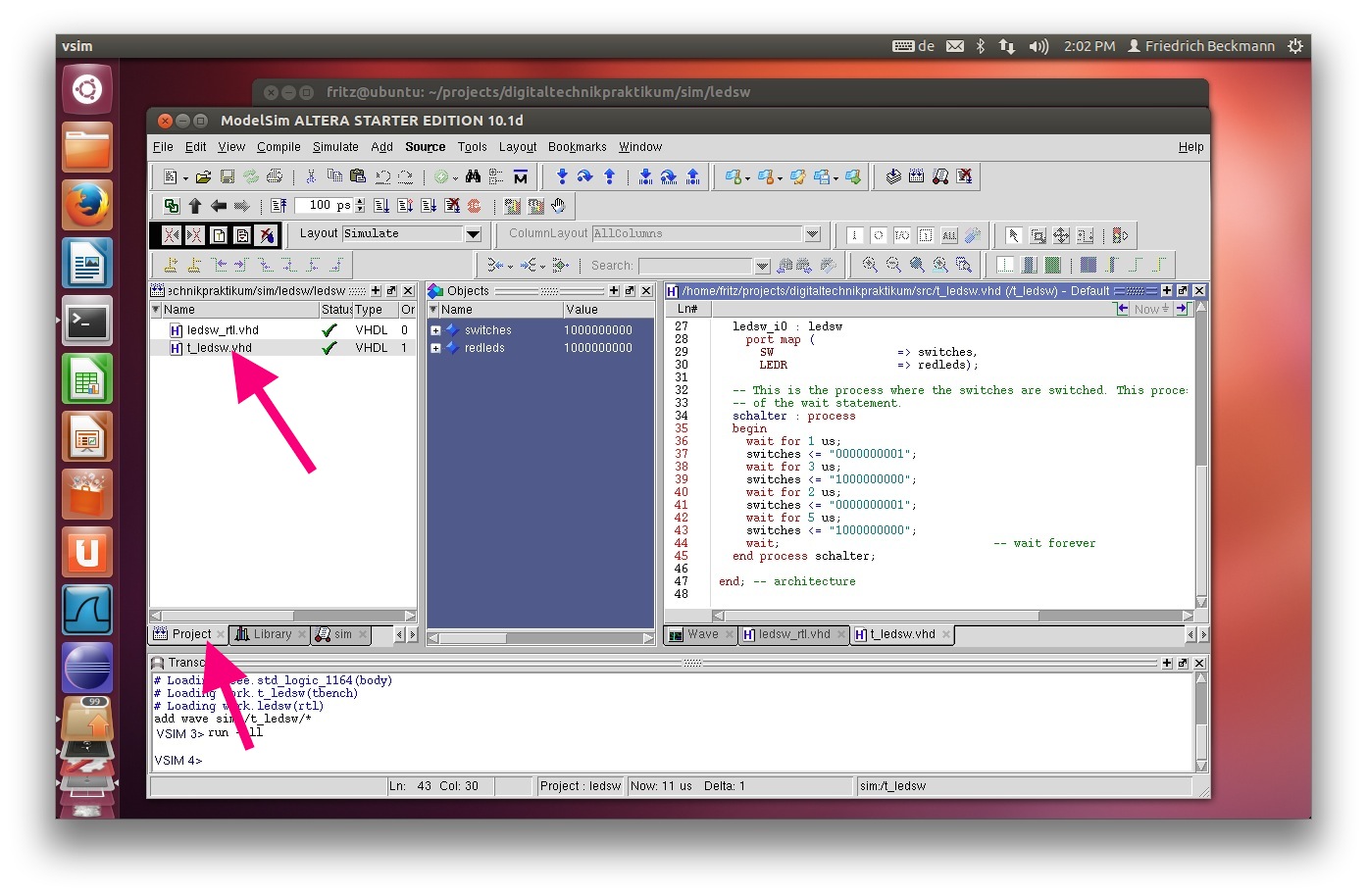

Gehen Sie dazu zurück in die Projektansicht und doppelklicken Sie auf “t_ledsw.vhd”.

Gehen Sie dazu zurück in die Projektansicht und doppelklicken Sie auf “t_ledsw.vhd”.

Jetzt ist das Editorfenster innerhalb von Modelsim geöffnet und Sie können den Inhalt der Datei ändern.

Jetzt ist das Editorfenster innerhalb von Modelsim geöffnet und Sie können den Inhalt der Datei ändern.

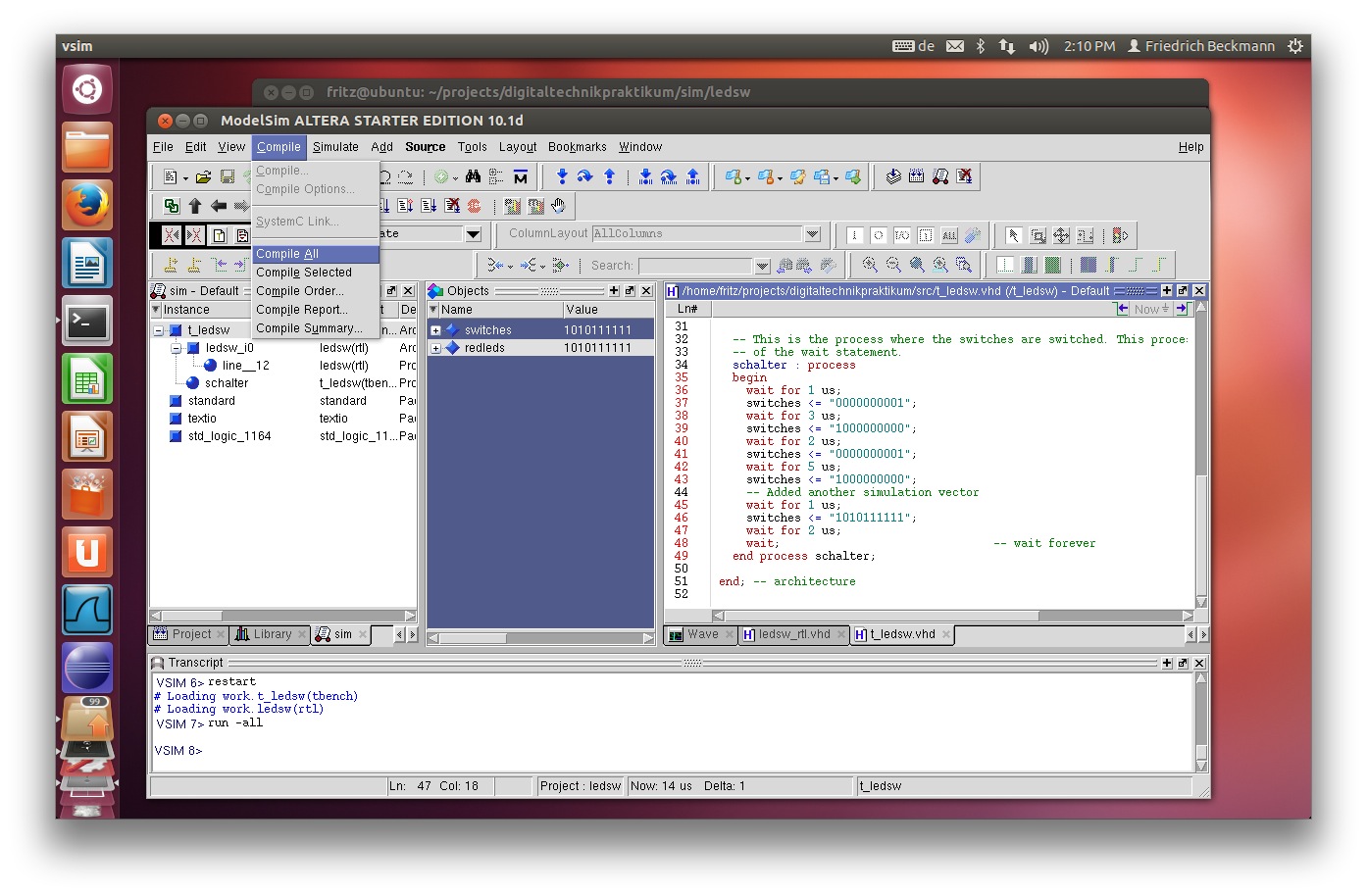

Nach der Änderung müssen Sie das Projekt neu kompilieren mit “Compile → Compile all”.

Nach der Änderung müssen Sie das Projekt neu kompilieren mit “Compile → Compile all”.

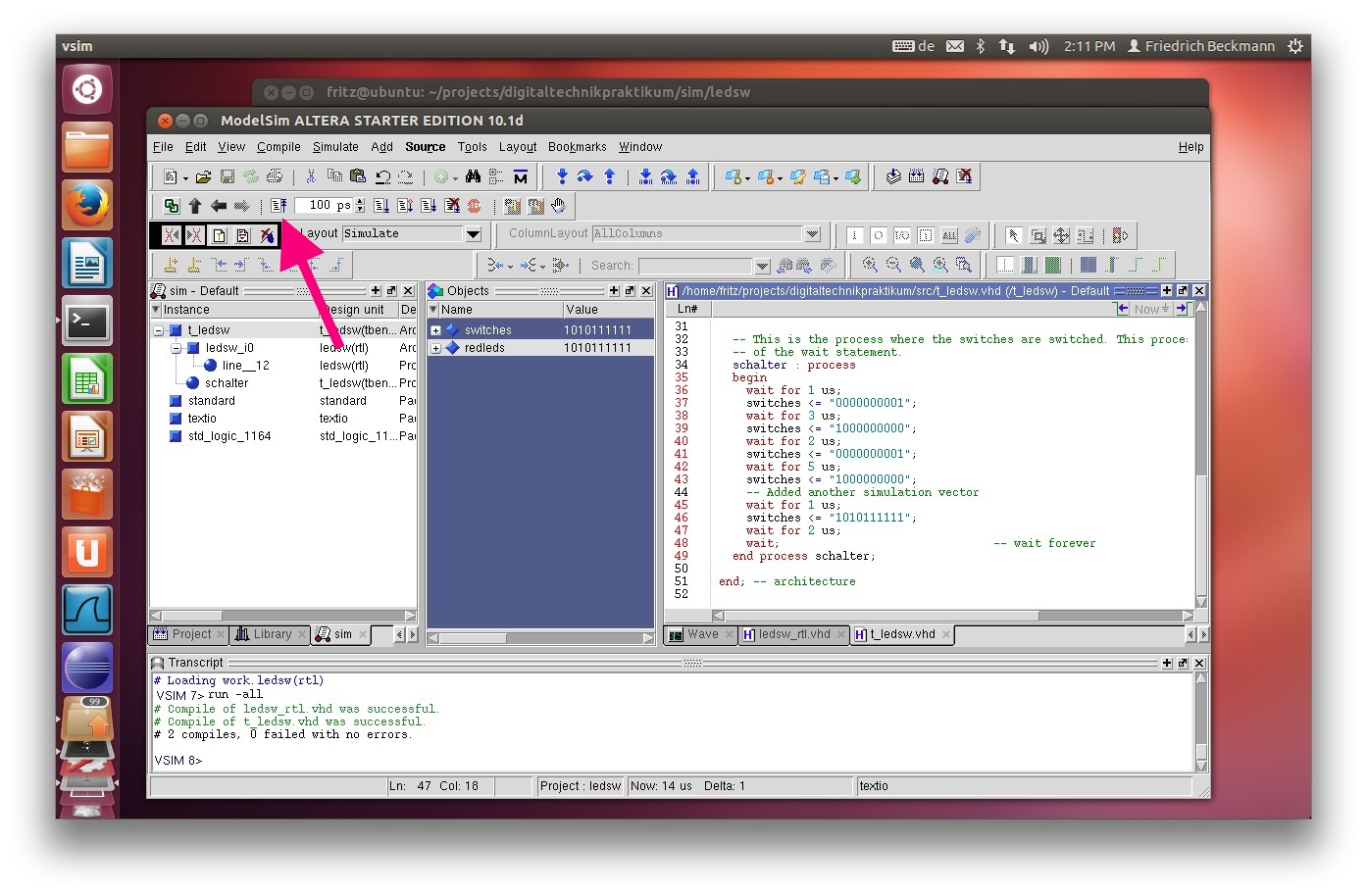

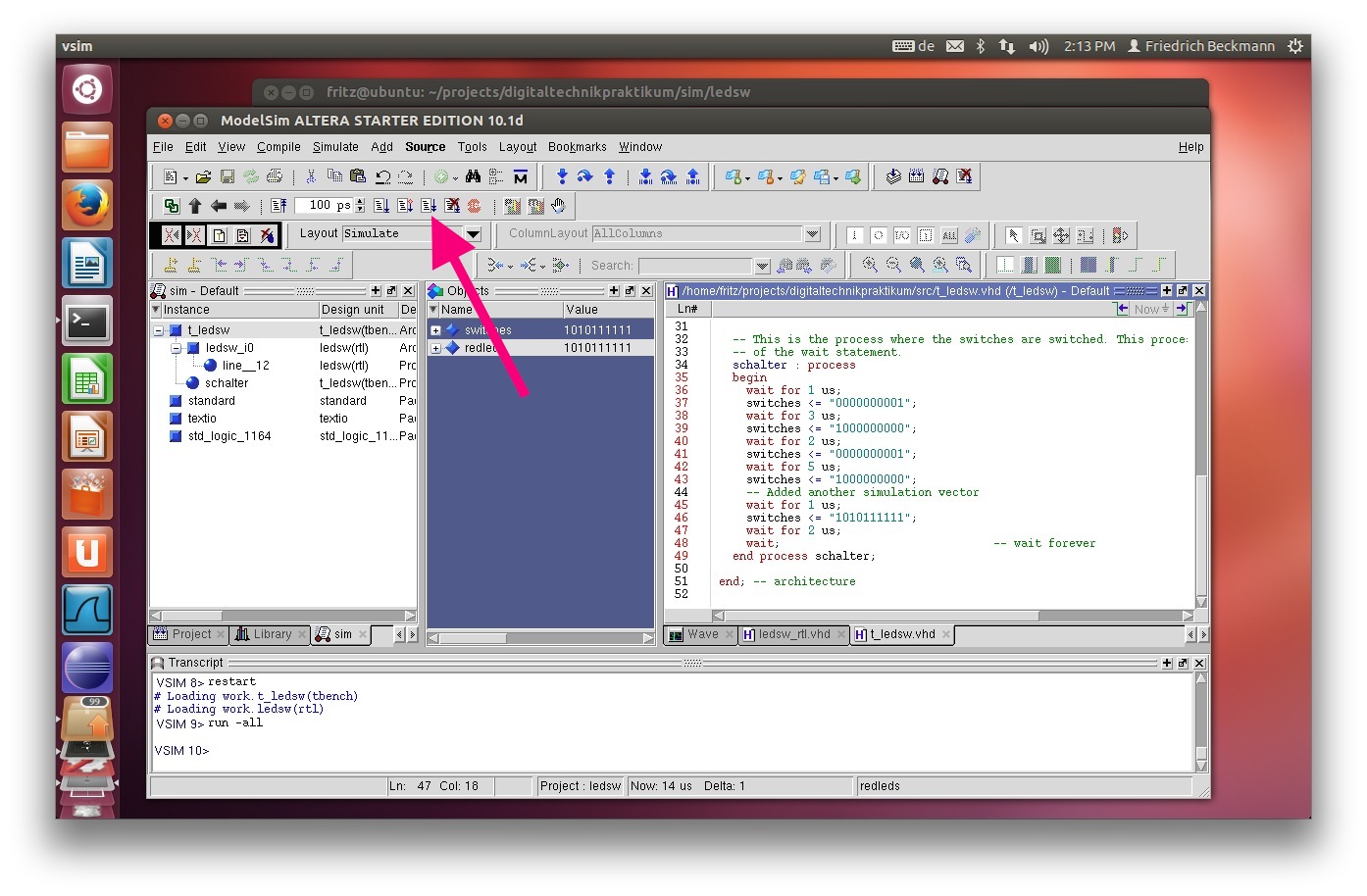

Danach müssen die Simulationsdaten neu geladen werden. Drücken Sie dazu auf den mit dem Pfeil markierten Knopf “Restart”. Alternativ können Sie auch über das Menü “Simulate → Restart” gehen.

Danach müssen die Simulationsdaten neu geladen werden. Drücken Sie dazu auf den mit dem Pfeil markierten Knopf “Restart”. Alternativ können Sie auch über das Menü “Simulate → Restart” gehen.

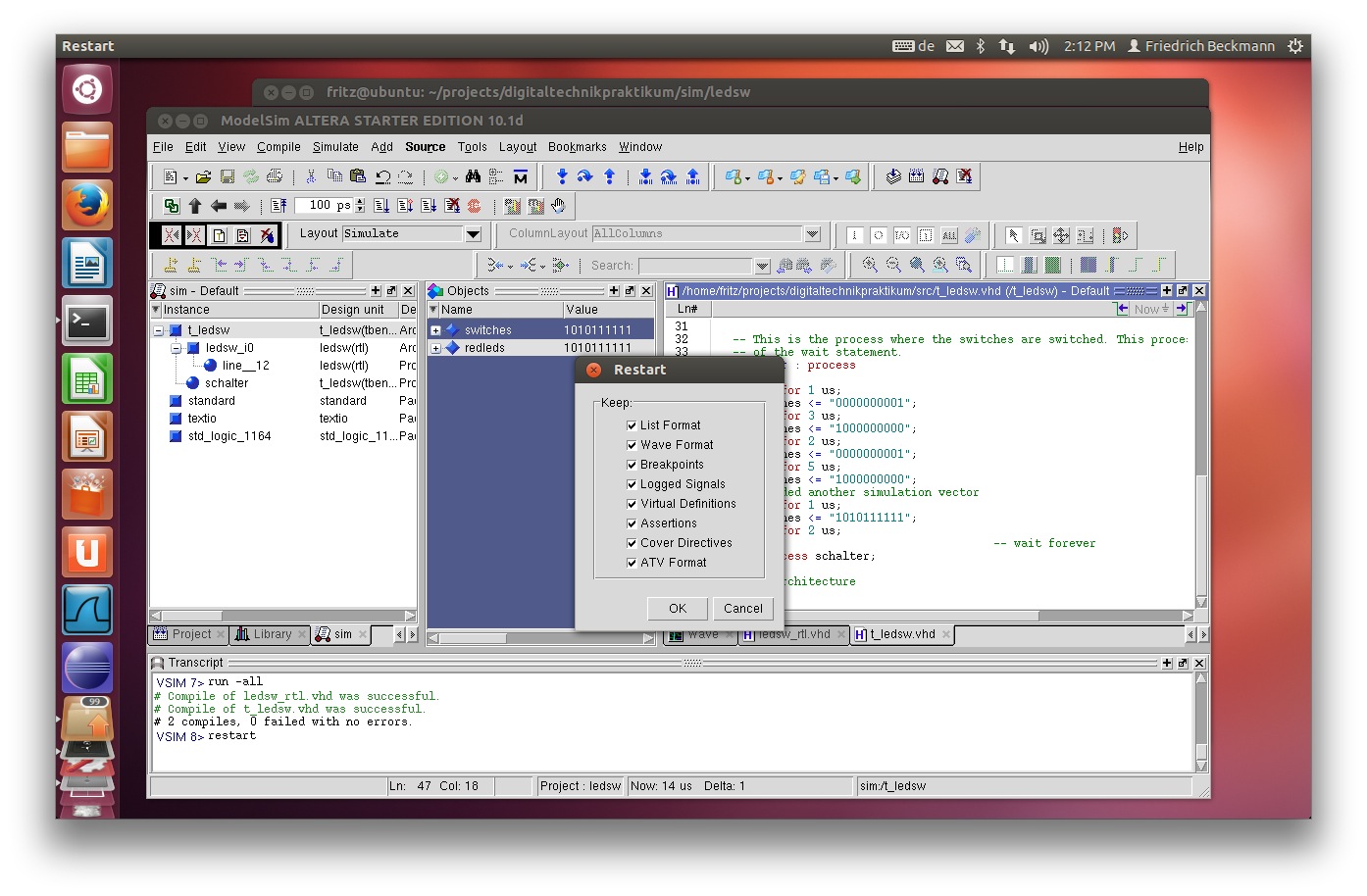

Es erscheint ein Dialogfenster zum Simulationsneustart. Drücken Sie auf “Ok”.

Es erscheint ein Dialogfenster zum Simulationsneustart. Drücken Sie auf “Ok”.

Jetzt ist die Simulation neu geladen und zurückgesetzt. Starten Sie die Simulation über den mit dem Pfeil markierten Knopf oder das Menü “Simulate → Run → Run -all”.

Jetzt ist die Simulation neu geladen und zurückgesetzt. Starten Sie die Simulation über den mit dem Pfeil markierten Knopf oder das Menü “Simulate → Run → Run -all”.

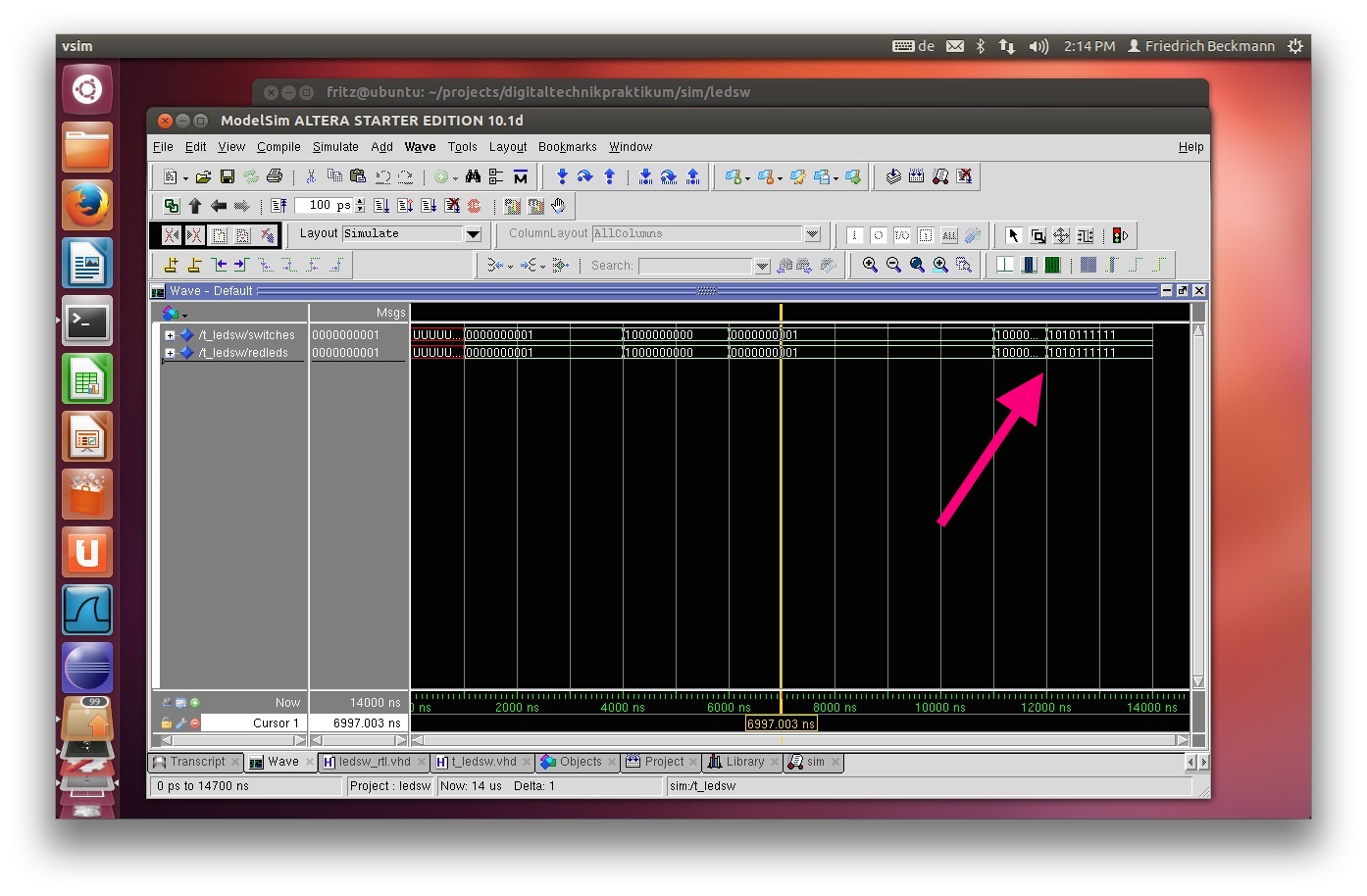

Wenn sie danach das Waveformfenster anschauen sehen Sie den zusätzlichen Simulationsvektor.

Wenn sie danach das Waveformfenster anschauen sehen Sie den zusätzlichen Simulationsvektor.

Simulation mit Modelsim - Aufsetzen des Projektes mit Make

Wie bei der Synthese mit Quartus kann auch die Simulation mit make gestartet werden.

cd cd digitaltechnikpraktikum cd sim cd ledsw

Wenn Sie im Simulationsverzeichnis einfach “make” eintippen, dann werden die möglichen make targets gezeigt.

fritz@ubuntu:~/projects/digitaltechnikpraktikum/sim/ledsw$ make "make" does intentionally nothing. Type: "make mproject" to create a new modelsim project only "make compile" to compile all VHDL sources in batch mode "make modelsim" to start modelsim with graphical user interface "make sim" to start modelsim gui with the top testbench of the project "make clean" to remove all generated files

Sie können das Projekt mit den zugehörigen Dateien aufsetzen und die graphische Benutzeroberfläche mit

make modelsim

starten. Wenn Sie gleich alle Toplevelsignale in das Waveformfenster übertragen und die Simulation starten wollen, dann können Sie das mit

make sim

Wenn ihr Code allerdings noch Fehler enthält, dann wird die graphische Oberfläche nicht gestartet. Sie können dann besser mit “make modelsim” die GUI starten und dann dort mit “Compile→Compile All” die VHDL Dateien übersetzen. Mit

make clean

werden alle temporär erzeugten Dateien gelöscht.

In der Datei makefile wird der Name des Projektes festgelegt. Aus dem Projektnamen wird ein Name für die Testbench nach dem Muster t_<project>.vhd abgeleitet. Zusätzlichen werden alle Dateien, die in der Datei makefile.sources aufgelistet sind, zu dem Projekt hinzugefügt. Hier müssen also alle Dateien aufgelistet werden, die zu dem Projekt gehören.

In dem Beispiel hier sind ist die Datei t_ledsw.vhd die Testbench und ledsw_rtl.vhd die Datei, die später für das FPGA synthetisiert wird.