Versuch 8

Drucken Sie die Checkliste dtpr-checkliste-v8.pdf aus.

Zustandsautomat syncsm

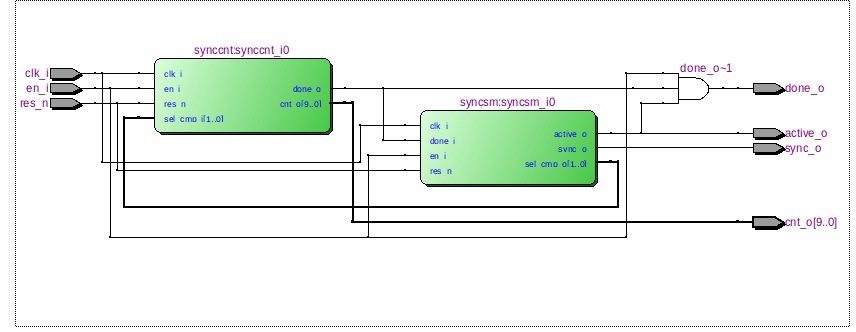

Bis jetzt haben Sie den steuerbaren Zähler synccnt entworfen. Jetzt sollen Sie den Zustandsautomaten syncsm entwerfen, der dann das sync, active und sel_cmp Signal erzeugt. Aus syncsm und synccnt wird dann der Sync Generator syncgen gebaut. In der Abbildung ist den sync Generator syncgen dargestellt.

Entwurfsphase

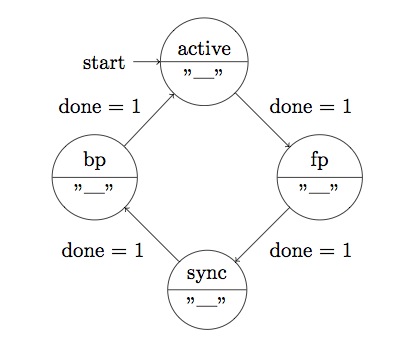

Sie kennen schon das Zustandsdiagramm mit den vier Zuständen des Automaten. In diesem Diagramm sind die Ausgangssignale noch nicht mit eingezeichnet.

- Stellen Sie eine Ausgangstabelle des Automaten auf, in der die Ausgangssignale in Abhängigkeit vom Zustand dargestellt ist.

- Stellen Sie eine Zustandsübergangstabelle für den Automaten auf.

Die Zustandsübergangslogik kann jetzt aus der Zustandsübergangstabelle abgeleitet und mit booleschen Gleichungen formuliert werden.

- Geben Sie die Zustandsübergangslogik und die Ausgangslogik als boolesche Gleichungen an.

- Skizzieren Sie Ihre Gesamtschaltung mit Speicher, Zustandsübergangslogik und Ausgangslogik.

Erklärphase

Erklären Sie einer anderen Gruppe Ihren Entwurf.

Designphase (syncsm, syncgen und vgatop)

Setzen Sie Ihren Entwurf in VHDL um.

Verifikationsphase

- Verifizieren Sie das Design im Simulator

- Verifizieren Sie das Design auf dem FPGA und messen Sie das hsync und vsync Timing

Umsetzung mit VHDL Automatencode

- Setzen Sie jetzt den Automaten mit VHDL um und verwenden Sie dazu die Beschreibung wie in play_rtl.vhd

- Verifizieren Sie den Automaten im Simulator

- Finden Sie mit Quartus die Anzahl der benötigten Flipflops für den Automaten heraus.