This is an old revision of the document!

Versuch 4

In diesem Versuch werden Zustandsautomaten als sequentielle Schaltungen eingeführt. Das Thema der sequentiellen Schaltungen wird vertieft.

Ziel des Versuchs

Das Ziel des Versuchs ist der systematische Entwurf von einfachen Zustandsautomaten auf Basis von Moore und Mealy, der Entwurf von gekoppelten Automaten und die Umsetzung in VHDL.

Die Flankenerkennung

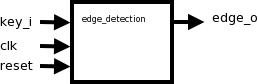

Im letzten Versuch wurde eine Flankenerkennung vorgestellt. In diesem Versuch soll die Flankenerkennung systematisch als Moore Automat entworfen werden. Die Flankenerkennung hat einen Eingang “key_i” und einen Ausgang “edge_o”. Die Flankenerkennung wird an den Zähler mit Enable aus dem letzten Versuch angeschlossen. Die Flankenerkennung wird dazu verwendet, jedesmal wenn die Taste “KEY(0)” gedrückt wird, den Zähler um eins hochzuzählen.

Die Flankenerkennung soll für die Dauer eines Taktes den Ausgang “edge_o” auf “1” setzen, wenn sich das Eingangssignal von “0” auf “1” ändert.

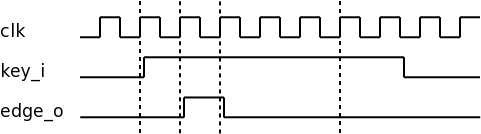

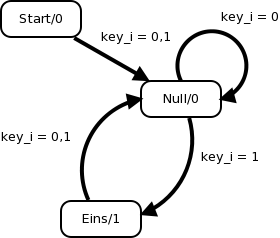

Das Timingdiagramm zeigt die gewünschte Funktion der Schaltung zur Flankenerkennung. Das Zustandsdiagramm ist im folgenden Bild dargestellt.

Der Automat hat drei Zustände: “Start”, “Eins” und “Null”. Der Automat startet nach dem Reset im Zustand “Start”. Das Ausgangssignal “edge_o” ist mit einem Schrägstrich “/” getrennt nach dem Zustandsnamen dargestellt. Der Automat bleibt im Zustand “Null”, wenn am Eingang “key_i” nur Nullen auftreten. Der Automat wechselt in den Zustand “Eins”, wenn er im Zustand “Null” ist und am Eingang “key_i” eine “1” erscheint. Aus dem Zustand “Eins” wechselt der Automat unabhängig vom Eingang in den Zustand “Null”. Der Ausgang “edge_o” geht auf “1”, wenn der Automat im Zustand “Eins” ist.

Der Zähler mit Enable aus dem letzten Versuch soll jetzt mit dem Zustandsautomaten zur Flankenerkennung gesteuert werden. Der Code ist hier zu finden:

Aufgaben Teil 1

- Legen Sie ein Verzeichnis “p1” an.

- Laden Sie den Code für die Flankenerkennung in das Verzeichnis “p1”.

- Kopieren Sie das Module “bin2seg.vhd” aus einem der vorherigen Versuche in dieses Verzeichnis.

- Simulieren Sie die Schaltung mit Modelsim

- Der VHDL Code in “edge.vhd” gibt das Zustandsdiagramm oben wieder. Erläutern Sie warum dieser Automat nicht wie gewünscht funktioniert und ändern Sie den Automaten so ab, dass er funktioniert. Zeichnen Sie das korrekte Zustandsdiagramm.

- Korrigieren Sie den Code in “edge.vhd” analog zu Ihrem neuen Zustandsdiagramm.

- Verifizieren Sie die Funktion im Simulator.

- Laden Sie das Design auf das FPGA und überprüfen Sie die Funktion auf dem FPGA.