This is an old revision of the document!

Praktikum Digitaltechnik - Versuch 4

Ziele:

In dieser Versuchseinheit stehen folgende Lernziele im Vordergrund:

- Entwicklung und vollständige Überprüfung einfacher Zustandsautomaten

- Kopplung von Zustandsautomaten

- Synchrone Standardelemente und -schaltungen einsetzen

- Aufbau von schnellen Zählern aus einem Schieberegister

Anerkennung als Studienarbeit

Zur Anerkennung dieses Praktikumsversuchs als Teilstudienleistung ist es notwendig, alle vorbereitenden Teilaufgaben und Laboraufgaben von den jeweiligen Betreuern mit Unterschrift auf dem Praktikumsprotokoll bestätigen zu lassen.

Theoretischer Hintergrund

Die bisher kennen gelernten Standardelemente und Entwurfstechniken sollen wiederholt und damit vertieft werden. Im Fokus steht hier aber die Entwicklung von Zustandsautomaten.

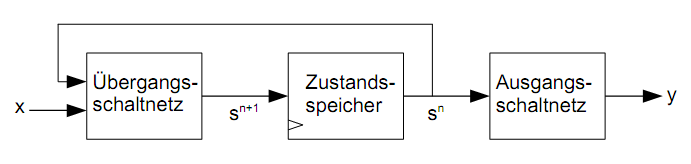

Da wir uns bewußt nur auf endliche Automaten vom Typ Moore beschränken, werden die Entwurfsregeln für synchrone Schaltungen noch um einen Punkt erweitert:

- Es gibt nur ein gemeinsames Taktsignal clk, welches an allen Takteingängen angeschlossen wird.

- Ein Taktsignal wird niemals über kombinatorische Elemente verknüpft.

- Jedes synchrone Modul besitzt ein asynchrones Rücksetzsignal, das nicht über kombinatorische Logikelemente geführt werden darf.

- Als Zustandsautomaten dürfen nur Moore-Maschinen eingesetzt werden.

Das Blockdiagramm eines Moore-Automaten ist nachfolgend nochmal abgebildet.

Außerdem wird ein Ansatz zur Entwicklung und Überpüfung einfacher Zustandsautomaten unter Verwendung eines Zustandsmaschineneditors gezeigt.

2-Bit Modulo-3 Abwärtszähler

Automatendiagramme (engl. State Machine Diagram) können mit Hilfe des Zustandsmaschineneditors QFSM sehr einfach erstellt werden. QFSM bietet außerdem verschiedene Möglichkeiten, um aus der grafischen Darstellung in verschiedene Beschreibungssprachen zu exportieren.

Entwurf

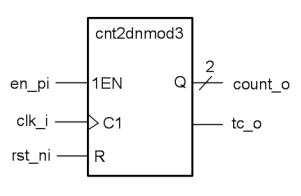

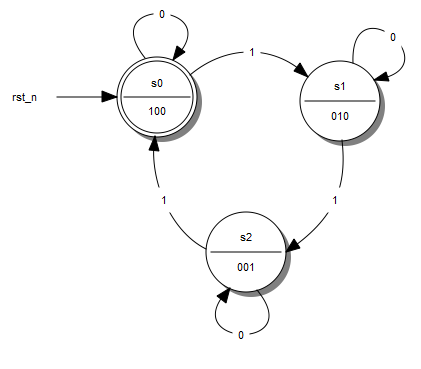

Nachfolgend sind Symbol und Zustandsdiagramm eines 2-Bit Modulo-3 Abwärtszählers cnt2dnmod3 dargestellt. Nach dem obligatorischen asynchronen Reset (durch rst_n) in den Zustand s0 ist der Zählzyklus 2, 1, 0. Dabei wird bei Erreichen des Zählwerts 0 das Ausgangssignal tc_o auf '1' gesetzt.

Ohne Legende ist es nicht einfach bis unmöglich, das Diagramm zu interpretieren. Welche Eingangssignale stehen an den Zustandsübergängen ? Welche Bedeutung haben die einzelnen Bits in den Zuständen ? Deshalb ist es immer notwendig, eine Legende, welche direkt aus QFSM erstellt werden kann, zu erzeugen.

Inputs: en_pi State/Output tc_o count_o[1] count_o[0] s0 1 0 0 s1 0 1 0 s2 0 0 1

Beim Export der VHDL-Beschreibung steht die Legende nochmals als Kommentar am Anfang des Quellcodes.

- cnt2dnmod3_qfsm.vhd

-- Inputs: en_pi -- State/Output tc_o count_o[1] count_o[0] -- s0 1 0 0 -- s1 0 1 0 -- s2 0 0 1 LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; ENTITY cnt2dnmod3 IS PORT (clk : IN std_ulogic; rst_n : IN std_ulogic; en_pi : IN std_ulogic; tc_o : OUT std_ulogic; count_o : OUT std_ulogic_vector(1 DOWNTO 0)); END cnt2dnmod3; ARCHITECTURE qfsm OF cnt2dnmod3 IS TYPE state_type IS (s0, s1, s2); SIGNAL next_state, current_state : state_type; BEGIN state_register : PROCESS (rst_n, clk) BEGIN ...

Verifikation

Zur vollständigen Verifikation einer Zustandsmaschine ist es notwendig, alle Zustandsübergänge zu durchlaufen, d.h. zu stimulieren. Dies geschieht am besten systematisch.

stimuli_p : PROCESS BEGIN WAIT UNTIL rst_n = '1'; -- wait until asynchronous reset ... -- ... is deactivated -- Complete Verification of State Machine means: stimulate every transition: -- Transition 0 en_pi <= '0'; -- deactivate enable input en_pi WAIT FOR period; -- Transition 1 en_pi <= '1'; -- activate enable input en_pi WAIT FOR period; -- Transition 2 en_pi <= '0'; -- deactivate enable input en_pi WAIT FOR period; -- Transition 3 en_pi <= '1'; -- activate enable input en_pi WAIT FOR period; -- Transition 4 en_pi <= '0'; -- deactivate enable input en_pi WAIT FOR period; -- Transition 5 en_pi <= '1'; -- activate enable input en_pi WAIT FOR period; clken_p <= false; -- switch clock generator off WAIT; -- suspend process END PROCESS;

WAIT-Anweisungen in Testbenches

In VHDL erfolgen Wertzuweisungen an Signale über ein sogenanntes Transaktionskonzept. Signalaktualisierungen erfolgen erst dann, wenn alle im vorherigen Simulationszyklus aktivierten Prozesse abgearbeitet wurden und wieder in einen Wartezustand übergegangen sind.

Da aufgrund von Entwurfsregeln nur synchrone Maschinen entwickelt werden dürfen, erfolgen in der Verifikation im Simulator (wie auch im Prototypentest) alle Signalzuweisungen synchron. Damit kann als Referenz eine vorher definierte Periode verwendet werden, wie in obigem Stimulusprozess stimuli_p.

en_pi <= '1'; -- activate enable input en_pi WAIT FOR period;

Syntax:

WAIT [FOR time_expression]; -- stoppt die Prozessabarbeitung für die angegebene Zeitdauer

Beispiele:

WAIT FOR 5 NS; WAIT FOR period; WAIT FOR period / 2; WAIT FOR 6 * period;

Syntax:

WAIT; -- warte für immer, beendet somit den Prozess (engl. suspend)

Beispiel:

WAIT; END PROCESS;

Syntax:

WAIT [ON signal_name_1] {,signal_name_n}; -- warte, bis sich ein Signalwert in der Liste ändert

Beispiele:

WAIT ON tc_o;

Syntax:

WAIT [UNTIL condition]; -- unterbricht die Prozessbearbeitung solange, bis die Bedingung erfüllt ist

Beispiele:

WAIT UNTIL falling_edge(clk_i); WAIT UNTIL rising_edge(clk_i); WAIT UNTIL count_o = "1001";

Vorbereitetung

Alle nachfolgend beschriebenen Aufgaben müssen wieder vor dem Versuchstermin bearbeitet werden.

Laden Sie sich den QFSM Zustandsmaschineneditor aus dem Downloadbereich für CAD Tools und installieren Sie dieses auf Ihrem persönlichen Computer. Alternativ können Sie die Installation in den PC-Räumen des Rechenzentrums unserer Hochschule nutzen.

Arbeiten Sie die Kurzanleitung zu QFSM durch.

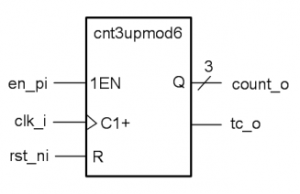

3-Bit Modulo-6 Aufwärtszähler

Mit Hilfe des Zustandsmaschineneditors QFSM soll ein 3-Bit Modulo-6 Aufwärtszähler cnt3upmod6 entwickelt werden. Im Gegensatz zu einem Abwärtszähler, bei dem das Terminal Count Signal tc_o bei erreichen des Zählwerts 0 gesetzt wird, ist bei einem Aufwärtszähler der maximale Zählwert (hier: der dezimale Wert 5) das Kriterium zum Setzen von tc_o.

Die Hierarchie des Zählermoduls:

t_cnt3upmod6(tbench) cnt3upmod6(qfsm)

- Zeichnen Sie mit QFSM das Zustandsdiagramm und speichern es in

src/cnt3upmod6.fsmim QuellcodeverzeichnisDigitaltechnikPraktikum/srcab.

- Exportieren Sie daraus eine VHDL-Beschreibung in die Datei

DigitaltechnikPraktikum/src/cnt3upmod6_qfsm.vhd.

- Egänzen Sie die Testbench

DigitaltechnikPraktikum/src/t_cnt3upmod6.vhdund führen Sie mit ModelSim eine vollständige Verifikation der Maschine durch. Stellen Sie in der Simulationsausgabe auch den aktuellen Zustand (SIGNAL current_state) dar.

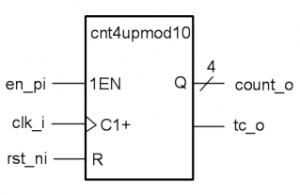

4-Bit Modulo-10 Aufwärtszähler

Mit Hilfe des Zustandsmaschineneditors QFSM soll ein 4-Bit Modulo-10 Aufwärtszähler cnt4upmod10 entwickelt werden.

Gehen Sie bei der Entwicklung des Moduls in den gleichen Schritten vor, wie bei dem Modul 3-Bit Modulo-6 Aufwärtszähler.

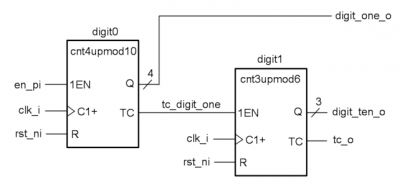

Zweistelliger Dezimalzähler

Aus den obigen Zählerblöcken kann nun ein Dezimalzähler für zwei Stellen (Einer- und Zehnerstelle) erstellt werden. Da dieser als Sekundenzähler verwendet werden soll, hat er einen Zahlenraum von 0 .. 59.

Die Hierarchie des Zählermoduls:

t_decimal_upcounter(tbench)

decimal_upcounter(structure)

cnt3upmod6(qfsm)

cnt4upmod10(qfsm)

- Verbinden Sie im Architecture Body

structuredes Entwurfs decimal_upcounter die beiden Zählermodule wie oben gezeigt.

- Ergänzen Sie den Prozess

stimuli_pder Testbench t_decimal_upcounter, um einen vollständigen Zählzyklus zu simulieren.

- Der vollständige Zählzyklus soll auch im Prototypentest auf dem DE1-Board mit dem Logikanalysator gemessen werden. Die Ein-/Ausgangssignale müssen dazu in der Testumgebung de1_decimal_upcounter an folgende General Purpose I/Os geführt werden:

Connector GPIO_1: GPO_1[3:0] = digit_one_o GPO_1[6:4] = digit_ten_o GPO_1[7] = tc_o GPO_1[8] = clk_i

Verkehrsampel - Vereinfachte Version 0.1

Zähler werden in der Regel nicht mit Hilfe von Zustandsdiagrammen konstruiert, unser Ansatz beruht auf didaktischen Überlegungen. Für die Modellierung von Zählern gibt es in VHDL abstrakte und leistungsfähige Konstrukte, die sich an die Methode aus Versuch 3 (Inkrementer und Zustandsregister) anlehnen.

Ein klassisches Beispiel für den Entwurf von Zustandsmaschinen stellt eine Verkehrsampel dar.

Die vier Ampelphasen

- Rot

- Rot und Gelb

- Grün

- Gelb

werden zyklisch durchlaufen. Vereinfacht kann damit jeder Phase ein Zustand in einem Zustandsdiagram zugewiesen werden:

Die Legende für die Ein-/Ausgangssignale des Zustandsdiagramms:

Inputs: next_phase_en_pi Output: red_o yellow_o green_o

Diese erste Version soll auf dem Prototypenboard DE MAX II Micro Kit (= DE-nano) realisert werden. Das Board besitzt ebenfalls einen Taktgenerator mit 50 MHz und acht verschiedenfarbige LEDs, geeignet für unsere Ampelanlage. Wir verwenden davon

LED4 = Rot LED3 = Gelb LED2 = Grün

Die Hierarchie der einfachen Ampelsteuerung zum Prototypentest:

demmk_traffic_light(structure) traffic_light(qfsm)

- Erstellen Sie mit QFSM das Zustandsdiagramm

traffic_light-v0.1.fsmmit Export in die DateiDigitaltechnikPraktikum/src/traffic_light_qfsm.vhd

- Beim Prototypentest im Labor soll schrittweise über den Taster Button2 von einer Ampelphase in die nächste geschaltet werden, Button1 wird als asynchroner Reset verwendet.

- Zeichnen Sie ein Blockschaltbild basierend auf dem Prototypentest

DigitaltechnikPraktikum/src/demmk_traffic_light_structure.vhd, das die Verbindung der Taster (Button1 und 2) und LEDs mit dem Ampelmodul zeigt.

- Von einer Verifikation im Simulator wird hier abgesehen.

Laboraufgaben

Zunächst haben Sie die Gelegenheit, mit den Betreuern die aufgetretenen Fragen und Probleme bei der Vorbereitung zu klären.

Messung: Dezimalzähler am Logikanalysator

- Projektverzeichnis

DigitaltechnikPraktikum/pnr/de1_decimal_upcounter

- Überprüfen Sie die Funktion des Dezimalzählers mit Hilfe des Logikanalysators. Messen Sie dabei das Taktsignal und alle Ausgangssignale. Stellen Sie einen vollständigen Zählzyklus dar.

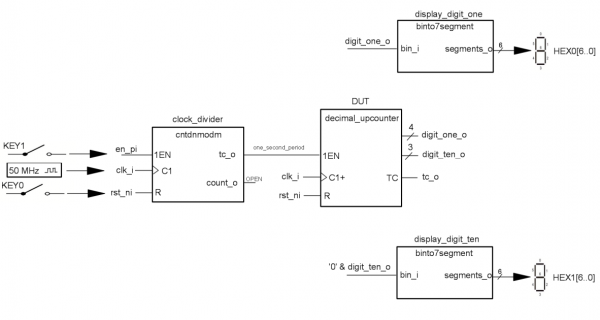

Dezimalzähler an 7-Segmentanzeige

Für den Einsatz als Sekundenzähler an zwei 7-Segmentanzeigen ist wieder das Frequenzteilermodul cntdnmodm aus Versuch 3 notwendig.

- Projektverzeichnis

DigitaltechnikPraktikum/pnr/de1_decimal_upcounter_1sec

- Führen Sie einen Prototypentest durch, welches Ihren vorher verifizierten Dezimalzähler verwendet. Stellen Sie sich folgenden Fragen:

- Funktioniert Ihr Zähler wie erwartet ?

- Welche Informationen benötigen Sie, um den Fehler genauer zu analysieren ?

- Worin unterscheidet sich dieser Prototypentest im Vergleich zum vorangegangenen ?

- Zur genaueren Analyse des Problems bietet sich das Simulationswerkzeug an. Modifizieren Sie die Testbench t_decimal_upcounter, indem Sie das Frequenzteilermodul cntdnmodm mit den Parametern n=3, m=4 an den Aktivierungseingang en_pi des Dezimalzähler anschließen.

- Warum werden hier andere Parameter (n=3, m=4) statt im Prototypentest verwendet ?

- Führen Sie damit eine erneute Simulation durch. Stellen Sie zusätzlich das interne Signal

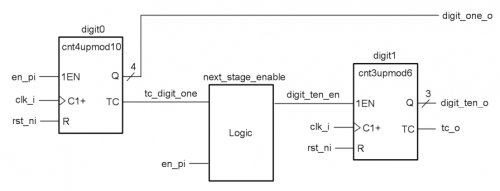

tc_digit_onedar. - Was passiert hier bei einem Übertrag von der Einer- auf die Zehnerstelle ?

Die bisherige einfache Verknüpfung der Zählerstufen reicht hier leider nicht aus. Die Module müssen über einen Logikblock verbunden werden, damit der Übertrag von einer auf die nächste Stufe korrekt funktioniert.

- Nachdem Sie das Problem verstanden haben, ergänzen Sie im Dezimalzählermodul decimal_upcounter die notwendige Logik zur Verbindung der Zählerstufen und verifizieren erneut im Simulator.

- Schließlich sollte das richtige Verhalten auch im Prototoypentest de1_decimal_upcounter_1sec bestätigt werden.

Verkehrsampel - Version 0.1

- Projektverzeichnis

DigitaltechnikPraktikum/pnr/demmk_traffic_light

- Erstellen und übersetzten Sie das Quartus-Projekt mit

$ make compile

- Starten Sie die grafische Benutzeroberfläche von Quartus mit dem Ampelprojekt

$ make quartus

- Starten Sie den Programmer, setzen Sie darin die Haken bei den Optionen Program/Configure und konfigurieren Sie damit das CPLD mit der Version 0.1 Ihrer Verkehrsampel auf dem Prototypenboard DE MAXII MicroKit (= DE-nano).

- Können Sie mit dem Button2 von einer Ampelphase in die folgende schalten ?

Verkehrsampel - Version 0.2

Im Unterschied zur ersten einfachen Version sollen die Rot- und Grünphasen hier länger sein.

Zusätzlich müssen die Phasen auf Basis einer Sekunde selbständig durchlaufen werden.

- Projektverzeichnis

DigitaltechnikPraktikum/pnr/demmk_traffic_light_1sec

- Erstellen Sie mit QFSM das Zustandsdiagramm

traffic_light-v0.2.fsmmit Export in die DateiDigitaltechnikPraktikum/src/traffic_light_qfsm.vhd

- Quellcodedatei für den Prototypentest ist

DigitaltechnikPraktikum/src/demmk_traffic_light_1sec_structure.vhd. Zeichnen Sie davon das Blockdiagramm auf Papier.

Die Hierarchie der erweiterten Ampelsteuerung zum Prototypentest:

demmk_traffic_light_1sec(structure) traffic_light(qfsm) cntdnmodm(rtl)

- Durchlaufen Sie alle Entwurfsschritte bis zum Prototypentest.

Hinweise zu den Aufgaben des nächsten Versuchstermins

Am Ende jedes Labortermins werden Ihnen von den Betreuern noch einige Hinweise zu den Aufgaben des nächsten Versuchs gegeben.