This is an old revision of the document!

Digitaltechnik Praktikum Versuch 6 - VGA Signal

In diesem ersten Versuch geht es um die Analyse des VGA Signals mit dem Logikanalysator und den Entwurf einer Schaltung zur Erzeugung des horizontalen Synchronisationssignals.

Vorbereitung

Zur Vorbereitung des Versuchs müssen Sie sich in die Funktion der VGA Schnittstelle vertraut machen. Die folgenden Links beschreiben die Funktionsweise der VGA Schnittstelle.

http://en.wikipedia.org/wiki/Video_Graphics_Array

http://lslwww.epfl.ch/pages/teaching/cours_lsl/ca_es/VGA.pdf

http://www.tinyvga.com/vga-timing/640x480@60Hz

Im DE1 Usermanual

https://www.hs-augsburg.de/~haf/secure/prototypeboards/DE1_UserManual_v1018.pdf

ist die Verschaltung des VGA Anschlusses FPGA in Kapitel 4.6 dargestellt. Die Funktion dieser Verschaltung ist hier

http://www.javiervalcarce.eu/wiki/Binary-Weighted_Digital_To_Analog_Converter

beschrieben.

Fragen zur Vorbereitung

- Wozu dient ein VGA Anschluss? Was kann man an einen VGA Anschluss anschliessen?

- Was wird über die drei Anschlüsse R, G und B über den VGA Anschluss übertragen?

- Wie schnell können sich die Signale an R, G und B bei einer Videoauflösung von 640×480 ändern?

- Was sind die minimale und die maximale Spannung der R, G und B Signale?

- Was bedeutet Pixeltakt? Welche Frequenz hat der Pixeltakt bei einer Auflösung von 640×480 Punkten?

- Was passiert in einem Röhrenmonitor wenn das HSYNC Signal aktiv ist?

- Was passiert in einem Röhrenmonitor wenn das VSYNC Signal aktiv ist?

- Ist die Frequenz des HSYNC Signals größer oder kleiner als die des VSYNC Signals?

- Was ist die front porch und die back porch time?

- Ist die front porch time für das VSYNC Signal länger oder kürzer als die front porch time für das HSYNC Signal?

- Warum kann man die Länge des HSYNC Signals in Pixeln und die Länge des VSYNC Signals in Zeilen angeben?

- Was ist die typische Leitungsimpedanz eines VGA Kabels?

- Welche Spannung stellt sich am VGA Steckerpin R ein, wenn VGA_R0 bis VGA_R2 auf “L” und VGA_R3 auf “H” liegen? Die Namen beziehen sich auf Figure 4.11 im DE1 Usermanual.

- Welche Farbe wird ein Pixel haben, wenn alle Signale VGA_R(3..0), VGA_G(3..0), VGA_B(3..0) auf “L” liegen?

- Welche Farbe wird ein Pixel haben, wenn alle Signale VGA_R(3..0), VGA_G(3..0), VGA_B(3..0) auf “H” liegen?

Laboraufgaben

Lassen Sie im Labor diese Checkliste V6 von den Betreuern abzeichnen.

Messung und Analyse eines unbekannten VGA Signals

Messung und Analyse in der Gruppe

Zunächst sollen die Signalverläufe eines unbekannten VGA Signals am Ausgang des DE1 FPGA Boards gemessen und analysiert werden. In dieser vga-messungen-fpga-belegung.zip Datei ist für jede Gruppe eine FPGA Belegungsdatei enthalten. Laden Sie FPGA Belegungsdatei für Ihre Gruppe über den Quartus Programmer auf das FPGA. Ihre Aufgabe ist die Messung und Analyse des Signals mit dem Oszilloskop und dem Logikanalysator. Beantworten Sie folgende Fragen und notieren Sie die Antworten auf einem Zettel. Begründen Sie Ihre Antworten! Skizzieren Sie die gemessenen Signalverläufe.

- Welche Polarität hat das VSYNC Signal? Ist es high- oder low-aktiv?

- Welche Polarität hat das HSYNC Signal? Ist es high- oder low-aktiv?

- Für welchen Zeitraum ist das VSYNC Signal aktiv?

- Für welchen Zeitraum ist das HSYNC Signal aktiv?

- Mit welcher Frequenz wiederholt sich das VSYNC Signal?

- Mit welcher Frequenz wiederholt sich das HSYNC Signal?

- Wie ist die Bildwiederholfrequenz?

- Wie viele Zeilen hat das VGA Signal pro Bild? Warum?

- Welche Auflösung hat das Bild?

- Geben Sie die front porch und back porch Zeit für das HSYNC Signal an.

- Geben Sie die front porch und back porch Zeit für das VSYNC Signal an.

- Skizzieren Sie den Amplitudenverlauf für die R, G und B Signale.

- Skizzieren Sie das Bild, das am Monitor erscheint, wenn Sie das FPGA an einen Monitor anschliessen. Geben Sie die Farben im Bild an.

Verifikation mit der Nachbargruppe

Nach der Messung, Analyse und Beantwortung der Fragen müssen Sie in der Lage sein einem Vertreter einer anderen Gruppe Ihre Antworten plausibel zu machen. Wählen Sie einen Vertreter aus Ihrer Gruppe, der in Ihrer Partnergruppe die Ergebnisse prüft. Jetzt werden die Gruppen gemischt und die Ergebnisse nochmal kontrolliert. Der “Prüfer” zeichnet die Ergebnisse der Partnergruppe ab. Warten Sie mit diesem Schritt bis alle Gruppen mit der Analyse fertig sind.

Anschluss eines VGA Monitors an das Board

Wenn Sie mit Ihrer Ausarbeitung fertig sind, wird der VGA Monitor an das FPGA angeschlossen und das erwartete Bild mit dem Monitorbild verglichen.

Entwurf einer Schaltung zur Erzeugung des horizontalen Synchronisationssignals (HSYNC)

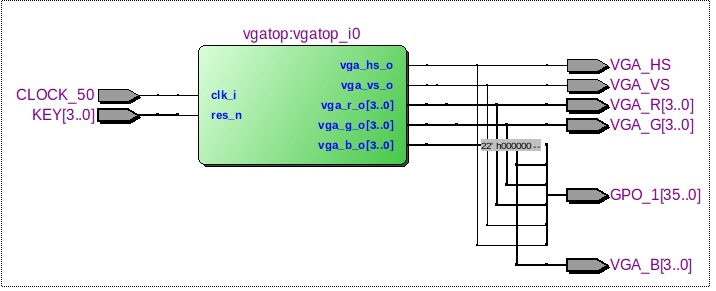

Jetzt sollen Sie einen Entwurf für einen HSYNC Generator machen, der das VGA_HS Signal für den VGA Anschluss erzeugt. Das Bild soll eine Auflösung von 640×480 Punkten und eine Bildwiederholfrequenz von etwa 60 Hz haben. Auf dem FPGA Board soll das 50 MHz Taktsignal genutzt werden.

Der Entwurf soll zunächst komplett auf dem Papier erfolgen. Versuchen Sie bei Ihrem Entwurf einen Ausblick für die Erzeugung des VSYNC Signals und die RGB Signale zu geben. Für den Entwurf sollen ausschliesslich die folgenden Komponenten verwendet werden. Andere, komplexere Komponenten müssen Sie auf Basis der aufgeführten zulässigen Komponenten erstellen.

Zulässige Komponenten

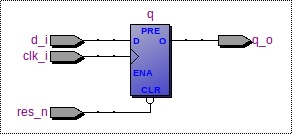

D-Flipflop

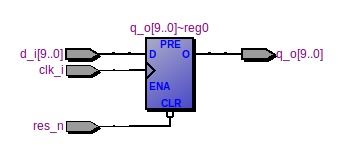

Register

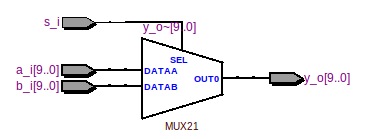

Multiplexer

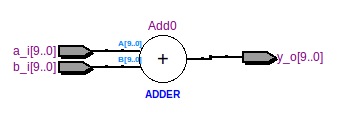

Addierer

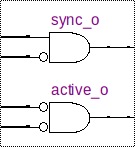

Logik auf Basis von booleschen Ausdrücken

Logik als Resultat von beliebigen booleschen Ausdrücken in VHDL.

-- Beispiel sync_o <= a and not(b); active_o <= not(a) and not(b); y_o <= not(a and not(b)) xor c;

Vorgehen

- Arbeiten Sie in Ihrer Gruppe einen Entwurf aus. Im Entwurf müssen Schaltpläne und geeignete Timingdiagramme enthalten sein. Sie müssen in der Lage sein, anderen Gruppen den Entwurf zu erläutern. Einigen Sie sich auf einen Gruppensprecher, der den Entwurf vorstellt. Kontaktieren Sie in dieser Zeit nicht die anderen Gruppen. (45 min)

- Jeweils vier Gruppen bilden ein Plenum und diskutieren die Entwürfe untereinander. Jede Gruppe stellt dazu Ihren Entwurf den anderen Gruppen vor (5 min). Danach wird der Entwurf diskutiert (5 min).

- Wählen Sie im Plenum einen Entwurf aus, der dem anderen Plenum vorgestellt werden soll

- Definieren Sie gegebenenfalls noch notwendige Änderungen, Ergänzungen und Verbesserungen, die in der Diskussion aufgefallen sind. (10 min)

- Dieser überarbeitete Entwurf wird dann dem anderen Plenum vorgestellt (5 min) und diskutiert (5 min).