This is an old revision of the document!

Versuch 7

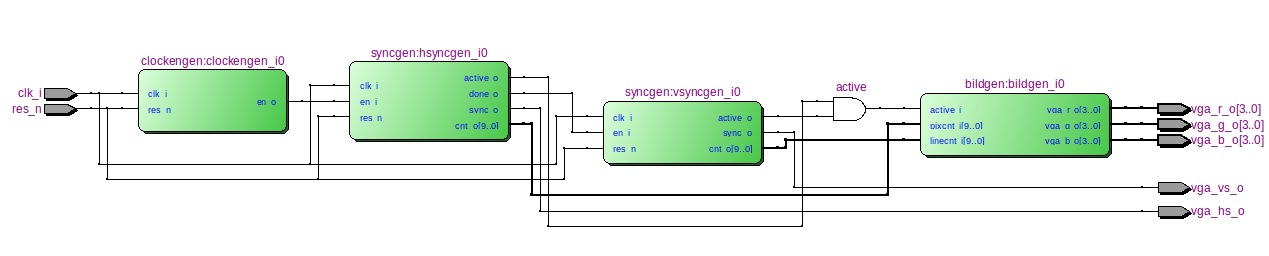

Beschreibung der Zielarchitektur des Systems

Taktschema

Der genaue Pixeltakt des Systems bei einer Auflösung von 640×480 Punkten beträgt 25,175 MHz. Dieser Takt ist ohne PLL nicht genau zu treffen. Deshalb wird ein Pixeltakt von 25 MHz gewählt. Dazu werden alle Schaltungsteile mit 50 MHz getaktet und mit einem Enablesignal mit 25 MHz Frequenz jeweils für jeden zweiten Takt aktiviert. Der resultierende Pixeltakt ist deshalb 25 MHz.

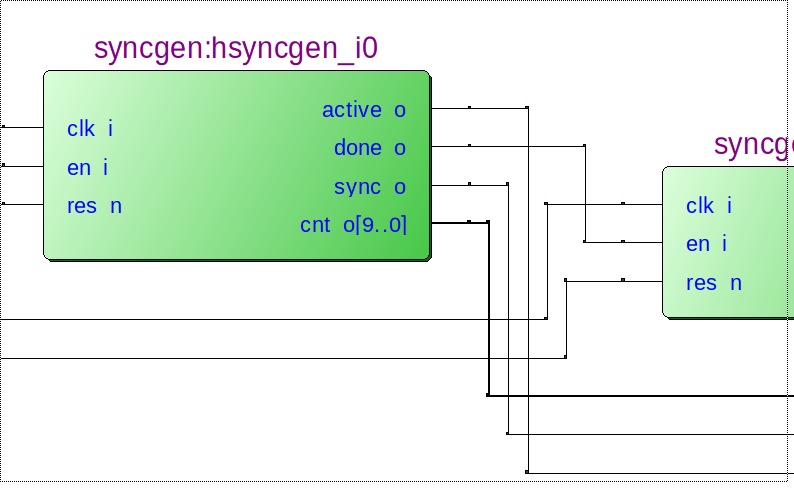

HSYNC Generator, VSYNC Generator und Bildgenerator

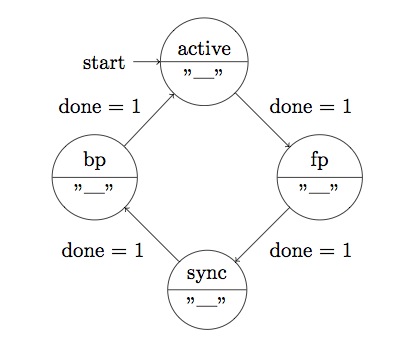

Der HSYNC Generator zählt die Pixel in einer Zeile im Pixeltakt hoch. Dazu wird das 25 MHz Enable verwendet. Der HSYNC Generator hat die Phasen

- Active

- Front porch

- Sync

- Back porch

Nach jeder Zeile zählt der VSYNC Generator eine Zeile weiter. Der VSYNC und HSYNC Generator sind identisch aufgebaut. Der VSYNC Generator erhält allerdings nur nach jeder Zeile ein Enablesignal. Dieses Enablesignal wird vom HSYNC Generator erzeugt. Die Zähler vom HSYNC und VSYNC Generator liefern den aktuellen Pixel und die aktuelle Zeile. Deshalb können diese Signale direkt vom Bildgenerator genutzt werden um die VGA Farbsignale zu erzeugen. Allerdings zählen die Zähler auch in den nicht aktiven Phasen (Front Porch, Sync und Backporch). Deshalb erhält der Bildgenerator zusätzlich die Information, dass sowohl HSYNC als auch VSYNC sich in der aktiven Phase befinden. Ansonsten wird an den Farbausgängen Schwarz ausgegeben.

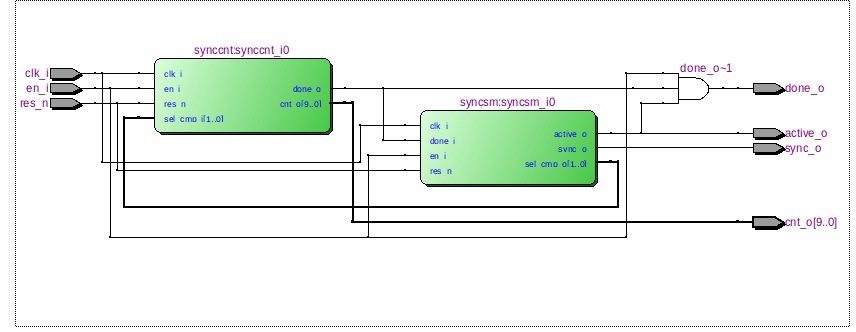

SYNC Generator Architektur

Der Sync Generator besteht aus dem Zähler “synccnt” und einem Automaten “syncsm”. Der Automat repräsentiert die Phasen des Generators. Der Zähler ist für die Dauer der Phasen des Automaten verantwortlich. Dazu produziert der Zähler ein “done” Signal, wenn der Zähler einen bestimmten Zählerstand erreicht hat. Bei welchem Zählerstand ein “done” Signal kommt, kann über das “sel_cmp_i(1..0)” Signal ausgewählt werden. Es gibt vier Vergleichswerte, die über “sel_cmp_i(1..0)” ausgewählt werden können. Wenn das “done” Signal aktiviert wird, wird gleichzeitig der Zähler auf 0 zurückgesetzt. Der Automat erzeugt das sel_cmp_i Signal und benutzt das “done” Signal um in die nächste Phase zu welchseln.

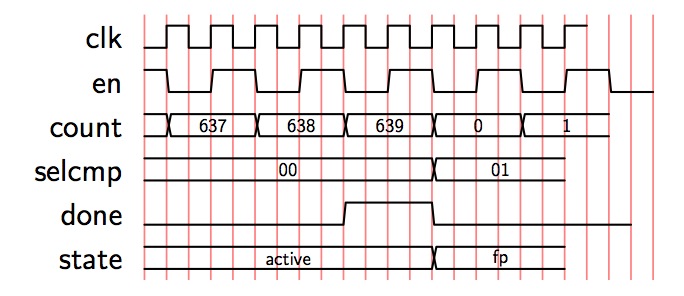

Die folgende Darstellung zeigt den Signalverlauf des Zählerstandes, des done Signals und des Zustands des Automaten:

In diesem Ausschnitt geht der Automat vom Zustand “active” in den Zustand “fp” über. Das “done” Signal wird bei einem Zählerstand von 639 aktiviert. Dieses Verhalten wird über die Wahl selcmp = “00” gesteuert. Mit der folgenden Phase “fp” wird das selcmp Signal auf “01” gesetzt.

In der folgenden Abbildung ist das Zustandsdiagramm des Automaten dargestellt.

Die Ausgangssignale des Automaten sind nicht eingezeichnet.

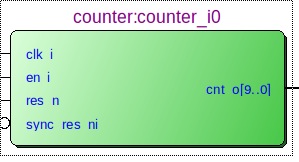

Synchron rücksetzbarer Zähler

Für den Zähler “synccnt” benötigen Sie als eine Komponente einen synchron rücksetzbaren Zähler mit Enable Eingang. Das Enablesignal soll höher priorisiert sein, als das synchrone Resetsignal.

Entwurfsphase

- Entwerfen Sie auf dem Papier mit Ihrer Gruppe einen synchron rücksetzbaren Zähler mit Enableeingang auf Basis der erlaubten Komponenten.

- Skizzieren Sie ein Timingdiagramm mit dem Synchronen Reset und dem Enablesignal.

Erklärphase

Jeweils vier Gruppen bilden ein Plenum.

- Stellen Sie im Plenum Ihren Entwurf vor. Erläutern Sie Ihr Timingdiagramm.

- Diskutieren Sie den Entwurf im Plenum.

Designphase

- Entwerfen Sie jetzt den Zähler in VHDL. Laden Sie dazu die vorbereiteten Designdaten dtpr-v7-counter.zip herunter.

- Simulieren Sie den Zähler mit der vorbereiteten Testbench in Modelsim.

Wenn Sie mit Ihrem Design fertig sind und es überprüft haben, stellen Sie die grüne Karte auf und bieten Sie anderen Gruppen Ihre Hilfe an.

Verifikationsphase

In dieser Phase stellt jede Gruppe einen “Prüfer”. Dieser Prüfer verifiziert das Design in einer anderen Gruppe. Jede Gruppe muss in der Lage sein dem Prüfer das eigene Design mit Designdaten, RTL Viewer und Simulationsergebnissen zu erläutern.

- Wählen Sie einen Prüfer in Ihrer Gruppe.

- Der “Prüfer” geht in eine andere Gruppe und prüft dort das Design. Der Prüfer zeichnet das Design auf dem Papierentwurf ab.

Zähler für den Sync Generator (synccnt)

Sie haben jetzt den synchron rücksetzbaren Zähler “counter”. Dieser Zähler soll als Komponenten für den “synccnt” Zähler verwendet werden, den Sie jetzt entwerfen und in VHDL umsetzen.

Entwurfsphase

Entwerfen Sie einen Zähler der bei einem steuerbaren Zählerstand ein “done” Signal aktiviert und im darauffolgenden Takt wieder bei 0 startet. Es sollen insgesamt vier Vergleichswerte mit dem Signal “sel_cmp_i(1..0)” wählbar sein.

Erklärphase

Erklären Sie einer anderen Gruppe Ihren Entwurf. Zeichnen Sie dazu Timingdiagramme.

Designphase

Setzen Sie jetzt das Design in VHDL um. Laden Sie dazu dtpr-v7-synccnt.zip auf Ihren Rechner.

Verifikationsphase

Wählen Sie einen “Prüfer” und lassen Sie Ihr Design von einem Prüfer einer anderen Gruppe überprüfen.