This is an old revision of the document!

Versuch 8

Zustandsautomat syncsm

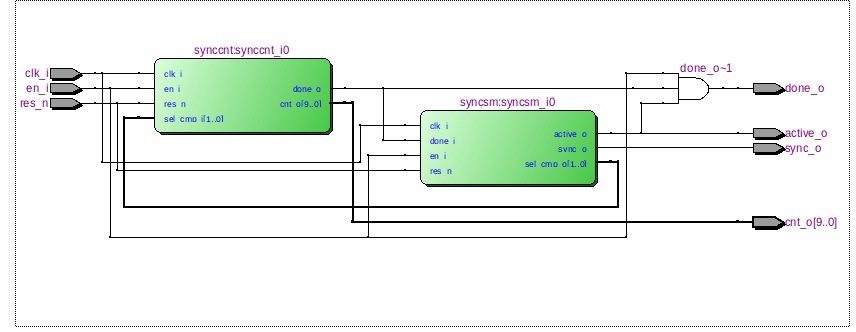

Bis jetzt haben Sie den steuerbaren Zähler synccnt entworfen. Jetzt sollen Sie den Zustandsautomaten syncsm entwerfen, der dann das sync, active und sel_cmp Signal erzeugt. Aus syncsm und synccnt wird dann der Sync Generator syncgen gebaut. In der Abbildung ist den sync Generator syncgen dargestellt.

Entwurfsphase

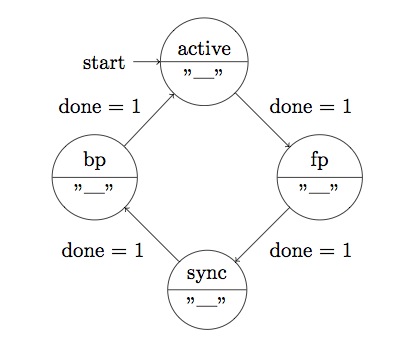

Sie kennen schon das Zustandsdiagramm mit den vier Zuständen des Automaten. In diesem Diagramm sind die Ausgangssignale noch nicht mit eingezeichnet.

- Stellen Sie eine Ausgangstabelle des Automaten auf, in der die Ausgangssignale in Abhängigkeit vom Zustand dargestellt ist.

- Stellen Sie eine Zustandsübergangstabelle für den Automaten auf.

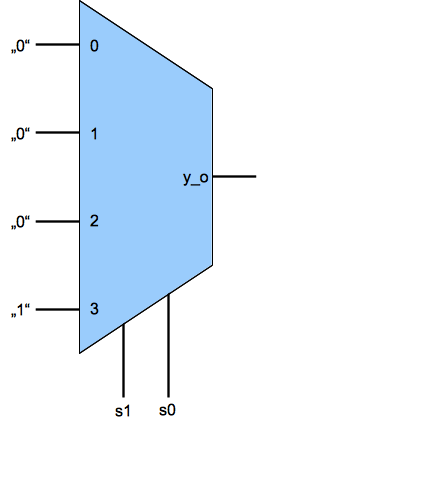

Die Zustandsübergangslogik könnte jetzt aus der Zustandsübergangstabelle abgeleitet und mit booleschen Gleichungen formuliert werden. Alternativ soll hier die Zustandsübergangslogik mit Hilfe eines Multiplexers umgesetzt werden. In der folgenden Abbildung

ist ein 4 zu 1 Multiplexer so mit Konstanten beschaltet, dass sich eine UND Funktion bezüglich der select Eingänge ergibt. Die Dateneingänge des Multiplexers können auch vom Typ std_ulogic_vector sein. Damit kann dann auch eine Logik mit mehreren Ausgängen beschrieben werden.

entity mux4 is generic ( width : integer); port ( d0_i : in std_ulogic_vector(width-1 downto 0); d1_i : in std_ulogic_vector(width-1 downto 0); d2_i : in std_ulogic_vector(width-1 downto 0); d3_i : in std_ulogic_vector(width-1 downto 0); s_i : in std_ulogic_vector(1 downto 0); y_o : out std_ulogic_vector(width-1 downto 0) ); end;

- Stellen Sie die Zustandsübergangslogik mit Hilfe eines Multiplexers mit konstanten Eingängen dar.

- Geben Sie die Ausgangslogik als boolesche Gleichungen an.

- Skizzieren Sie Ihre Gesamtschaltung mit Speicher, Zustandsübergangslogik und Ausgangslogik.

Erklärphase

Erklären Sie einer anderen Gruppe Ihren Entwurf.

Designphase

Setzen Sie Ihren Entwurf in VHDL um. Laden Sie dazu die folgenden Designdaten herunter dtpr-v8-syncgen.zip.

- Der synccnt Entwurf ist nicht vollständig. Kopieren Sie Ihren Entwurf in das src Verzeichnis.

- Der syncgen Entwurf ist schon fertig, d.h. die Verbindung von synccnt und syncsm.

- Fügen Sie das syncgen Modul in den vgatop ein und konfigurieren Sie die Zähler so, dass das hsync Signal korrekt erzeugt wird.

Verifikationsphase

Laden Sie Ihr Design auf das FPGA und verifizieren Sie das Timing des HSYNC Signals.