Kombinatorische Grundschaltungen mit FPGA und VHDL

Aufgabenstellung

Mit dem Altera DE 1 Board, der CAD Software und dem VHDL Projektverzeichnis starten Sie mit VHDL und steuern die roten und grünen LEDs auf dem Board abhängig von den Schaltern.

In der Vorbereitung installieren Sie die virtuelle Maschine und das Projektverzeichnis und nehmen eine Änderung am Code vor.

Vorbereitung

Installation der virtuellen Maschine

Die CAD Software mit

- Altera Quartus II Synthesesoftware

- ghdl VHDL Schaltungssimulator

- vscodium Editor

wird von Hans Färber in einer virtuellen Maschine unter Linux für Sie vorinstalliert. Laden und installieren Sie VirtualBox und die virtuelle Maschine auf Ihrem Rechner oder Laptop. Auf den Rechnern im Labor ist genau diese Maschine installiert.

Auf der Maschine ist

User: caeuser Password: caeuser

eingerichtet. Starten Sie die virtuelle Maschine und loggen Sie sich ein.

Starten eines Terminals und Einrichten des Projektverzeichnisses

Starten Sie ein Terminal mit “System Tools ⇒ QTerminal”

Jetzt haben Sie ein geöffnetes Terminalprogramm.

Überblick über einige Unix Shellbefehle

| Befehl | Beispiel | Beschreibung |

|---|---|---|

| ls | ls -la | Anzeige der Dateien im aktuellen Verzeichnis |

| pwd | pwd | Anzeige des Pfads vom aktuellen Verzeichnis |

| mkdir | mkdir projects | Erzeugen eines neuen Verzeichnisses “projects” |

| cd | cd | Wechsel Homeverzeichnis |

| cd | cd projects | Wechsel in das Verzeichnis “projects” |

| cd | cd .. | Wechsel in das höhere Verzeichnis ausgehend vom aktuellen Verzeichnis |

| man | man ls | Aufruf des Handbuchs für den Befehl “ls” |

| rm | rm hallo.txt | Löschen der Datei “hallo.txt” |

| less | less hallo.txt | Anschauen der Datei “hallo.txt”. Beenden mit “q” |

| vi | vi hallo.txt | Editor starten für die Datei hallo.txt |

Legen Sie nun das Verzeichnis “projects” an und wechseln Sie in das Verzeichnis

cd mkdir projects cd projects

Download des VHDL Projektverzeichnisses

Die VHDL Projektdateien sind auf dem gitlab Server der Fakultät Elektrotechnik. Laden Sie die Projektdateien über git in das Verzeichnis “projects”.

cd /home/caeuser/projects git clone https://gitlab.elektrotechnik.hs-augsburg.de/beckmanf/dtlab

Sie sollten nun die Projektdateien vom gitlab Server auch in Ihrem Verzeichnis haben

caeuser@CAE-Tools-OS:~/projects/dtlab$ cd ~/projects/dtlab caeuser@CAE-Tools-OS:~/projects/dtlab$ ls -la total 40 drwxr-xr-x 7 caeuser users 4096 Mar 7 12:35 . drwxr-xr-x 9 caeuser users 4096 Mar 6 20:35 .. drwxr-xr-x 8 caeuser users 4096 Mar 8 10:15 .git -rw-r--r-- 1 caeuser users 265 Mar 6 22:22 .gitignore drwxr-xr-x 5 caeuser users 4096 Mar 8 00:22 pnr -rw-r--r-- 1 caeuser users 1159 Mar 6 22:13 ReadMe.md drwxr-xr-x 2 caeuser users 4096 Mar 7 12:35 scripts drwxr-xr-x 3 caeuser users 4096 Mar 7 12:35 sim drwxr-xr-x 2 caeuser users 4096 Mar 8 00:28 src -rw-r--r-- 1 caeuser users 210 Mar 8 00:36 vhdl_ls.toml caeuser@CAE-Tools-OS:~/projects/dtlab$

Die Verzeichnisse haben folgenden Inhalt:

| Verzeichnis | Inhalt |

|---|---|

| pnr | Verzeichnis mit Unterordnern mit den Syntheseprojekten |

| scripts | Skripte für Simulation und Synthese - don't touch it |

| sim | Verzeichnis mit Unterordnern für die Simulationen |

| src | Verzeichnis mit den VHDL Dateien |

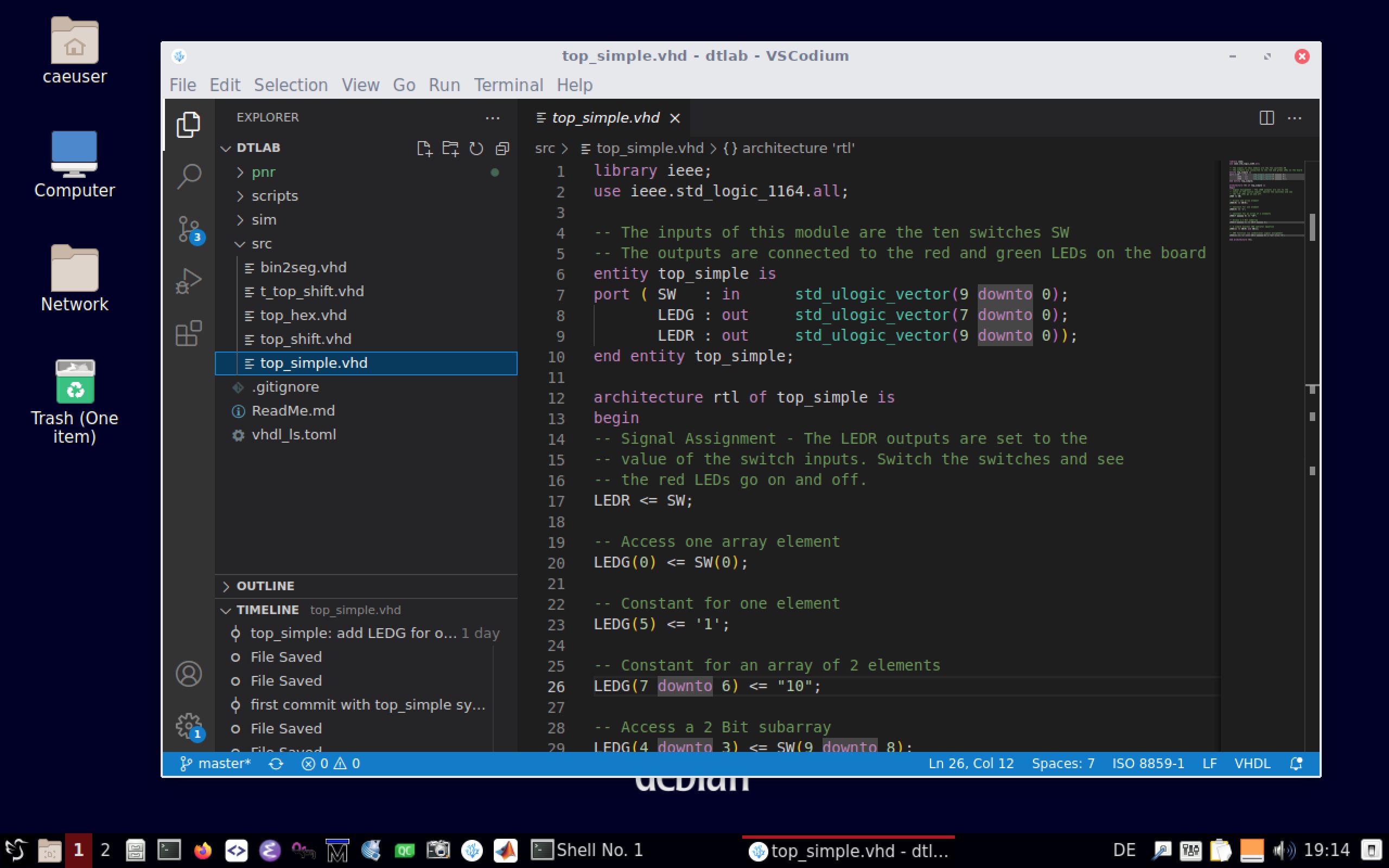

Start VSCodium

Öffnen Sie den Editor über “Programming ⇒ VSCodium”. Alternativ können Sie den Editor auch vom Terminal aus mit

codium

starten.

Öffnen Sie dann im Editor über “File ⇒ Open Folder” das Verzeichnis “projects/dtlab”.

Öffnen Sie dann über den VSCodium File Explorer die Datei “src/top_simple.vhd”.

Das sollte dann so aussehen

Die Datei VHDL Datei "top_simple.vhd" beschreibt die erste einfache Schaltung.

VHDL Entity und Architecture

Nach einer Einführung zu dem Konzept von Entity und Architecture dann die Entity und Architecture für “top_simple”.

VHDL Entity

Die VHDL Datei "top_simple.vhd" enthält eine “entity”.

entity top_simple is port ( SW : in std_ulogic_vector(9 downto 0); LEDG : out std_ulogic_vector(7 downto 0); LEDR : out std_ulogic_vector(9 downto 0)); end entity top_simple;

Die “entity” beschreibt die Ein- und Ausgänge der Schaltung. Die Funktion der Schaltung wird in der “architecture” beschrieben. Die Zeile

SW : in std_ulogic_vector(9 downto 0);

beschreibt einen Eingangsport mit dem Namen “SW”. Der Typ des Eingangsports ist “std_ulogic_vector(9 downto 0)”. Das ist ein Array mit 10 Leitungen vom Typ “std_ulogic”. “std_ulogic” ist eine Typdefinition und bedeutet, dass jedes Arrayelement des Ports SW im wesentlichen die logischen Werte 1 oder 0 annehmen kann. Wir haben also 10 Leitungen!

Die beiden Ausgangsports LEDG und LEDR haben 8 und 10 Leitungen. Man kann die Entity als Schaltungsmodul mit Ein- und Ausgängen auffassen. So eine grafische Darstellung ist in Abbildung 1 dargestellt.

Abb. 1: Entity top_simple mit dem Eingang SW und den Ausgängen LEDG und LEDR

Diese entity “top_simple” ist besonders, weil es die höchste Schaltungsebene “toplevel entity” auf dem FPGA beschreibt. Die Ein- und Ausgänge repräsentieren Pins auf dem FPGA Baustein. Auf dem Alteraboard sind diese Pins mit anderen Bauteilen verbunden. Im Boardschaltplan des Altera DE1 Boards kann man sehen, dass der Schalter SW0 mit dem Pin L22 verbunden ist. LEDR und LEDG sind mit den roten und den grünen LEDs verbunden.

VHDL Architecture

In der Architecture wird dann beschrieben welche Funktion die Schaltung haben soll

architecture rtl of top_simple is begin LEDR <= SW; LEDG(1) <= SW(0) and SW(1); end architecture;

In diesem Beispiel wird festgelegt, dass die 10 Ausgänge LEDR den Wert von den 10 Eingängen SW bekommen sollen. Dem Ausgangsport LEDG(1) wird das Ergebnis der UND Verknüpfung von SW(0) und SW(1) zugewiesen. Hier wird also die Funktion eines UND Gatters gebaut!

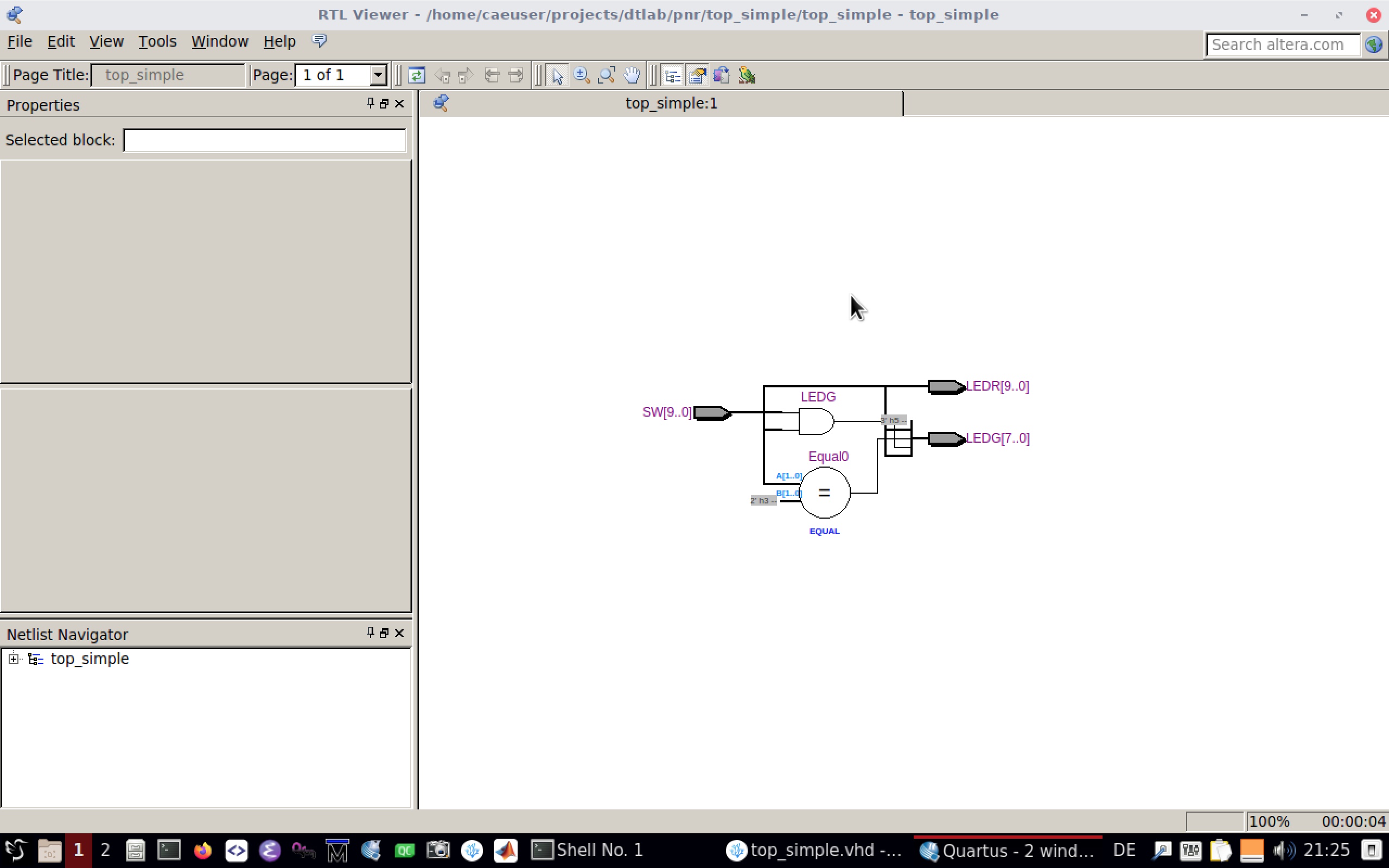

Altera Quartus Software / RTL Viewer

Der RTL Viewer in der Quartus Software erzeugt einen grafischen Schaltplan der die Struktur und die Funktion des VHDL Codes repräsentiert. Wechseln Sie in den Ordner für die Synthese von “top_simple”. Starten sie dort die Quartussoftware für den RTL View.

cd ~/projects/dtlab/pnr/top_simple make rtlview

Sie sollten dann die Quartus Software sehen

Öffnen Sie dann den “RTL Viewer” mit “Tools ⇒ Netlist Viewers ⇒ RTL Viewer”.

Sie sehen eine grafische Darstellung des VHDL Codes von “top_simple”. U.a. ist das UND Gatter zu sehen.

Altera Quartus Synthese und Download auf das FPGA

Anschluss des Boards an den Rechner / USB

Um die Konfiguration auf das FPGA zu laden, müssen Sie das Altera Board mit dem USB Kabel an den Rechner anschliessen. Wenn Sie das mit der virtuellen Maschine machen, müssen Sie bei VirtualBox das USB Interface vom Hostsystem in die virtuelle Maschine weiterleiten. Das müssen Sie machen, nachdem das Board mit dem USB Kabel an den Rechner angeschlossen wurde. Achten Sie auch darauf, dass das Board eingeschaltet ist. Üblicherweise leuchten einige LEDs. Leiten Sie dann das USB Interface in die virtuelle Maschine über das Menü von VirtualBox:

Geräte => USB Geräte => Altera USB-Blaster

Synthese und Download

Wechseln Sie in das Syntheseverzeichnis und starten Sie die Synthese und den Download

cd ~/projects/dtlab/pnr/top_simple make prog

Die Quartus Synthesesoftware stellt den Zusammenhang zwischen den Portnamen in der Entity “top_simple” und den Pins am FPGA über die Pinkonfigurationsdatei top_simple_pins.tcl her. Dort sehen Sie, dass dem Pin L22 der Portname SW(0) zugeordnet ist.

VHDL Code ändern

Sie können den VHDL Code in VSCodium ändern und dann neu synthetisieren und auf das Board laden. Bleiben Sie dazu im Terminal im Syntheseverzeichnis pnr/top_simple und geben Sie einfach neu

make prog

oder für den RTL Viewer

make rtlview

ein.

Probieren Sie dies einmal aus und ändern Sie die UND Funktion in eine XOR Funktion

LEDG(1) <= SW(0) xor SW(1);

Im RTL Viewer sollte dann ein XOR Gatter zu sehen sein und auf dem Board hat sich die Funktion an LEDG1 geändert.

Schaltplan zeichnen

Zeichnen Sie auf Papier (oder elektronischem Papier) einen Schaltplan, der das FPGA mit der Schaltung von top_simple darstellt. Bringen Sie den Schaltplan mit in das Labor.

Aufgaben

Ändern Sie den VHDL Code von top_simple.vhd so ab, dass die grünen LEDs folgende Funktion haben

LEDG7

soll leuchten, wenn mindestens ein Schalter eingeschaltet ist.

LEDG6

soll leuchten, wenn die Schalter 9..5 die gleiche Schalterstellung haben wie die Schalter 4..0.

LEDG5..0 ECC

Flashspeicher und auch RAM Speicher werden häufig mit zusätzlichen Fehlerkorrekturverfahren (englisch: ECC: Error Correcting Code oder Error Checking and Correction) betrieben. Dazu werden Prüfsummen von den Daten berechnet, die dann zusammen mit den Daten abgespeichert werden. In Samsung, NAND Flash ECC Algorithm, June 2004 wird ein solches Verfahren erläutert.

Auf Seite 3 “ECC Code Generation Example” wird das Verfahren für die Berechnung von sechs Prüfbits (P4´, P2´, P1´, P4, P2 , P1) für ein Datenwort mit acht Bit beschrieben.

Verwenden Sie dieses Vorgehen analog für die Berechnung der Prüfbits (P2´, P1´, P2 , P1) für ein 4 Bit Datenwort. Geben Sie die Prüfbits (P2´, P1´, P2 , P1) für die Berechnung der Daten auf den grünen LEDs LEDG[3..0] aus. Das Datenwort D[3..0] = “1011” sollte dann (P2´, P1´, P2 , P1) = “0110” ergeben. Mit P2´=D1 xor D0, P1´= D2 xor D0, P2=D3 xor D2 und P1 = D3 xor D1.

| D3 | D2 | D1 | D0 | |

|---|---|---|---|---|

| P2 | x | x | ||

| P2' | x | x | ||

| P1 | x | x | ||

| P1' | x | x |

Simulieren Sie jetzt einen Lesezugriff auf ein 4 Bit Datenwort mit den zugehörigen 4 Prüfbits mit den Schaltern. Die Datenbits sollen auf SW[3..0] und die gelesenen Prüfbits (P2´, P1´, P2 , P1) auf SW[7..4] sein. Durch Vergleich der aus den Daten SW[3..0] berechneten neuen Prüfbits mit den gelesenen Prüfbits an SW[7..4] kann man verschiedene Fehlersituationen bei der Annahme von einem Bitfehler unterscheiden.

| Situation | Erkennung |

|---|---|

| Kein Fehler | Die neu berechneten Prüfbits sind gleich den gelesenen an SW[7..4] |

| Korrigierbarer Fehler | Es unterscheiden sich genau zwei Prüfbits und es ändern sich nicht gleichzeitig P1 und P1´ oder P2 und P2´. |

| ECC Fehler (Ein Bit) | Genau ein Prüfbit unterscheidet sich |

| Nicht korrigierbar | Alles andere |

Signalisieren Sie das an LEDG[5..4].

| LEDG[5..4] | Bedeutung |

|---|---|

| 00 | Kein Fehler |

| 01 | Korrigierbarer Fehler |

| 10 | ECC Fehler |

| 11 | Nicht korrigierbarer Fehler |

Geben Sie an LEDR[7..4] das ggf. korrigierte Datenwort aus.

Hinweise VHDL

In top_simple.vhd gibt es nur Ausdrücke, die LEDR oder LEDG direkt aus SW berechnen. Sie können jedoch auch Zwischensignale einführen.

Signale

architecture rtl_new of top_simple is signal one_is_on : std_ulogic; begin one_is_on <= SW(0) xor SW(1); LEDR(0) <= one_is_on; end architecture;

selected signal assignment

Mit einem “selected signal assignment” kann man einem Signal oder einem Ausgangsport einen Wert in Abhängigkeit von einem anderen Signal oder Eingangsport zuweisen.

architecture rtl_new of top_simple is signal one_is_on : std_ulogic; begin with SW(2 downto 0) select one_is_on <= '1' when "001"|"010"|"100", '0' when others; LEDG(0) <= one_is_on; end architecture;

Labor

Stellen Sie Ihre Lösungen im Labor vor.