Table of Contents

Digitaltechnik Praktikum Versuch 2 - Kombinatorische Schaltung / Hierarchische Schaltung

Das Ziel dieses Versuchs ist die Beschreibung von kombinatorischen Schaltungen mit Hilfe von

- Booleschen Ausdrücken

- Conditional Signal Assignments

- with select Beschreibung

sowie die hierarchische Beschreibung von Schaltungen in VHDL. Als praktisches Beispiel werden Sie eine Schaltung entwerfen, die jeweils vier SW Schalter binär interpretiert als Ziffer an einer Siebensegmentanzeige anzeigt. Die Eingänge der Schaltung werden mit den Schaltern verbunden und die Ausgänge werden mit der Siebensegmentanzeige und den roten LED's verbunden. Wenn beispielsweise die Schalter SW3..SW0 auf “0101” stehen, dann soll die Ziffer “5” an der Siebensegmentanzeige angezeigt werden.

Projekt aktualisieren

Um ihre lokalen Projektdateien mit eventuellen neuen Dateien auf dem git Server zu aktualisieren können sie im Verzeichnis “digitaltechnikpraktikum”

git pull

eingeben. Dann werden neue oder geänderte Daten vom git server geladen. Wenn auf dem Server Änderungen an Dateien vorgenommen wurden für die Sie auch Änderungen vorgenommen haben, dann wird die pull Aktion abgebrochen. In diesem Fall müssen die Dateien zusammengeführt werden, allerdings können Sie auch ihre Änderungen verwerfen. Sie können ihre Änderungen verwerfen und den letzten Stand wiederherstellen mit

cd cd digitaltechnikpraktikum/src git checkout . cd ..

Danach sollte die pull Aktion funktionieren.

Beispiel ledcomb_rtl.vhd

Im Projektverzeichnis finden Sie als Beispiel für die Darstellung von kombinatorischen Schaltungen die Datei ledcomb_rtl.vhd. Dazu passend gibt es das Syntheseverzeichnis “pnr/ledcomb”.

Die Schaltung ledcomb hat als Eingänge die Schalter “SW”. Die Ausgänge sind die roten LEDs “LEDR” und die grünen LEDs “LEDG”. Die roten LEDs zeigen den Zustand der Schalter an. An den grünen LEDs werden verschiedene boolesche Funktionen dargestellt. In der Schaltung ledcomb gibt es weiterhin drei Signale s0, s1 und s2. Die Signale können wie Netze in einem Schaltplan verstanden werden.

- Skizzieren Sie die Schaltungen für die Ausgänge LEDG(0), LEDG(1), LEDG(2), LEDG(3)

- Für welche Schalterkombinationen leuchtet der Ausgang LEDG(0)?

- Für welche Schalterkombinationen leuchtet der Ausgang LEDG(1)?

- Für welche Schalterkombinationen leuchtet der Ausgang LEDG(2)?

- Für welche Schalterkombinationen leuchtet der Ausgang LEDG(3)?

- Für welche Schalterkombinationen leuchtet der Ausgang LEDG(4)?

- Skizzieren Sie die Schaltung für den Ausgang LEDG(4)

- Erläutern Sie wie die Ausgänge LEDG(7..5) von den Eingängen SW(9..6) abhängen.

Wechseln Sie jetzt in das Verzeichnis “pnr/ledcomb”, starten Sie die Schaltungssynthese und laden Sie das Design auf das FPGA Board.

- Zeigen Sie, dass die grünen LEDs LEDG(7..5) die Anzahl der eingeschalteten Schalter SW(9..6) als Binärzahl anzeigt.

- Wie und Warum unterscheiden sich die Dateien ledcomb_pins.tcl und ledsw_pins.tcl?

Analyse des Syntheseergebnisses

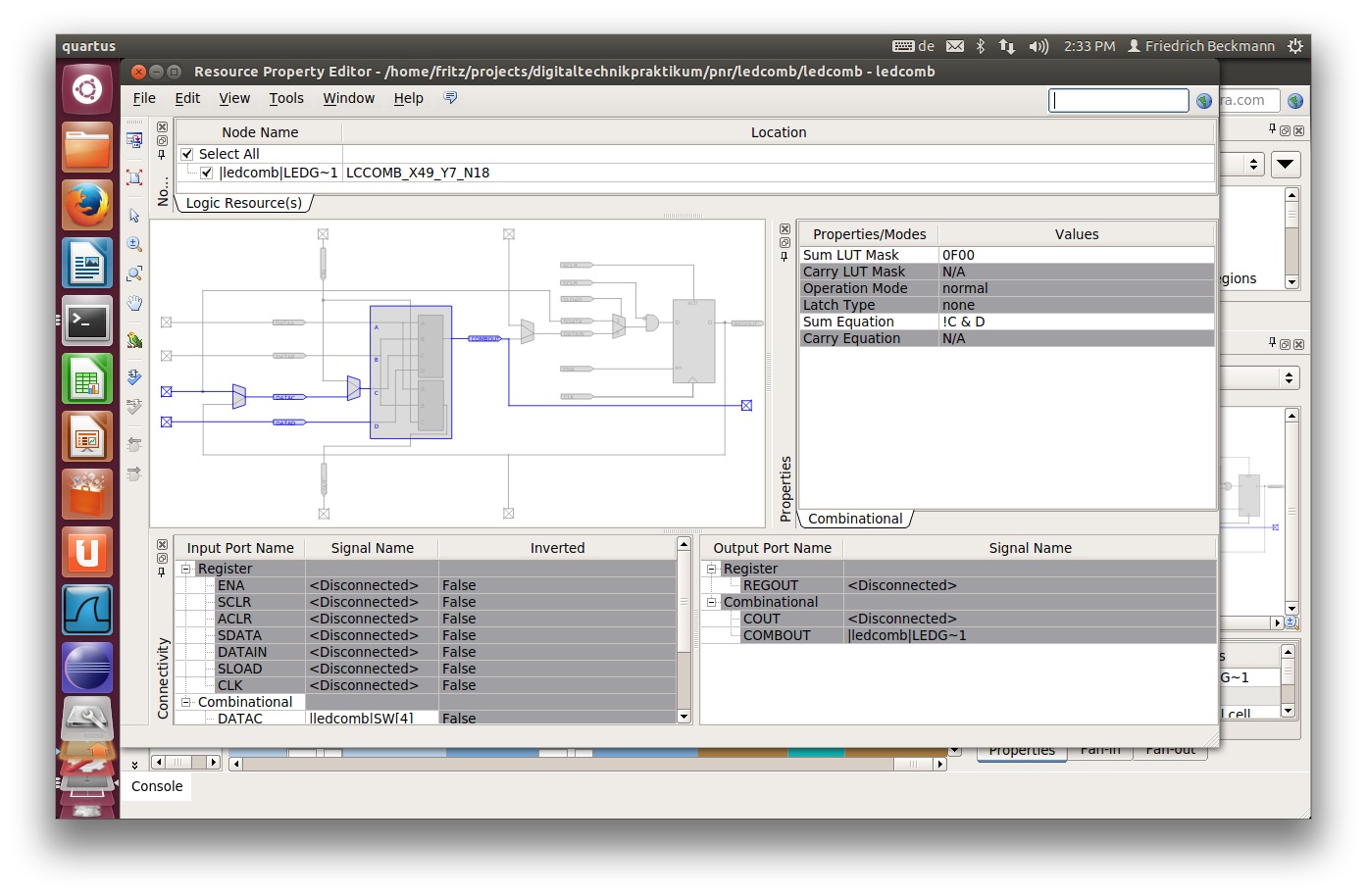

Die Quartussoftware erlaubt eine Analyse des Syntheseergebnisses. In Figure 2-1 im Cyclone II Datenblatt ist die Chipstruktur des FPGA dargestellt. Ein Großteil des FPGA besteht aus Logikelementen (LE), die konfigurierbar miteinander verbunden werden können. Ein Logikelement ist in Figure 2-3 im Datenblatt dargestellt. Mit der “Four-Input LUT” (eine Lookuptabelle mit 4 Eingängen) kann jede boolesche Funktion mit 4 Eingängen und einem Ausgang dargestellt werden. Im Logikelement befindet sich zusätzlich noch ein Flipflop, das in diesem Versuch nicht benutzt wird. Insgesamt befinden sich auf dem FPGA auf dem Board 18752 Logikelemente. Bei der Synthese müssen die Logikelemente konfiguriert werden, d.h. die boolesche Funktion der “Four-Input LUT” wird festgelegt, und die Logikelemente müssen miteinander verbunden werden.

Wechseln Sie in das Syntheseverzeichnis, starten Sie die Synthese und starten Sie die Quartus GUI.

cd cd digitaltechnikpraktikum/pnr/ledcomb make compile make quartus

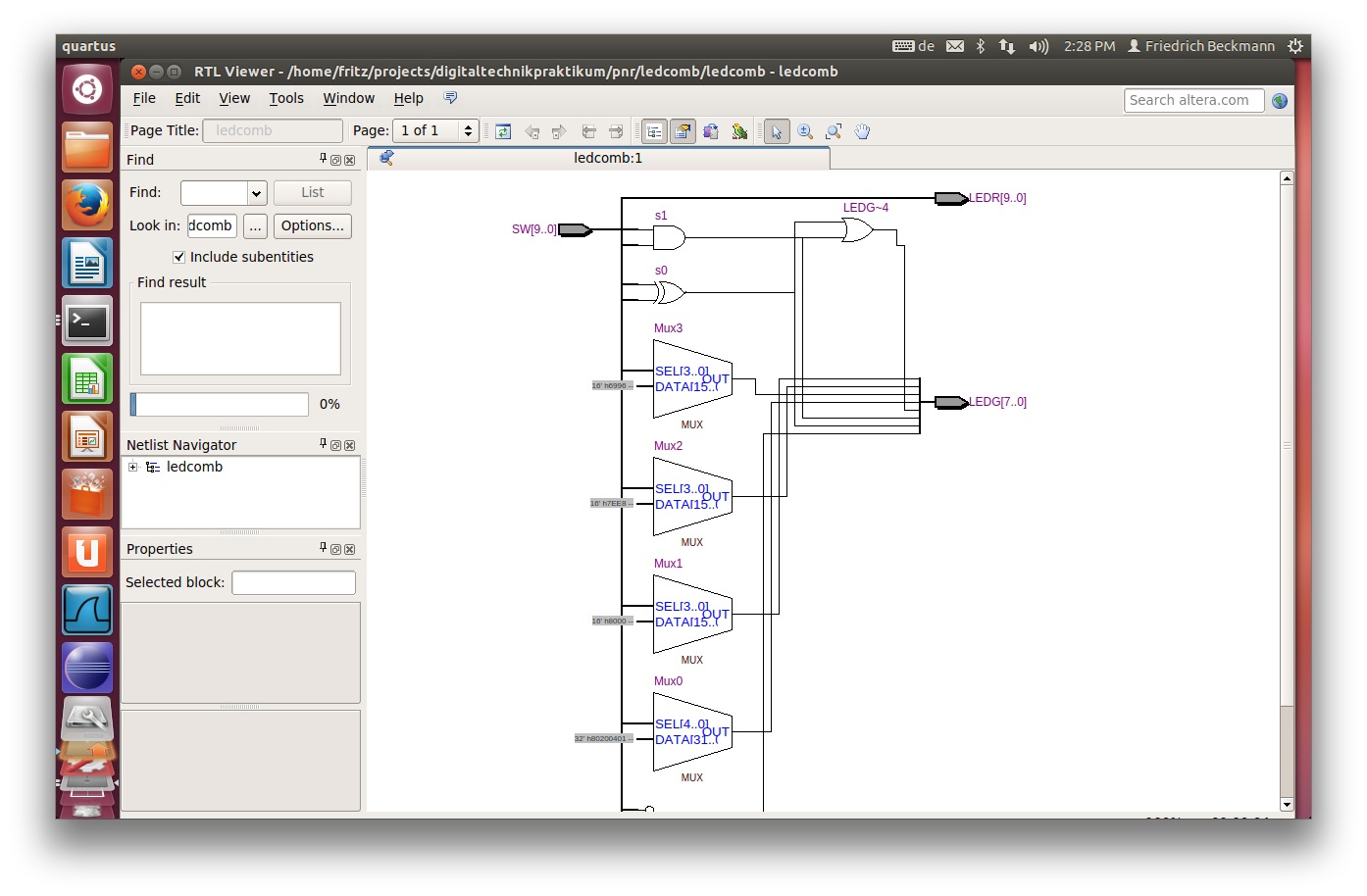

Starten Sie mit “Tools → Netlist Viewers → RTL Viewer” die graphische Darstellung Ihres VHDL Codes.

Sie können für die Ausgänge LEDG(0), LEDG(1), LEDG(2) und LEDG(3) die graphische Darstellung der booleschen Gleichung sehen. Sie können die zusammengefassten Ports wie SW(9..0) auch als einzelne Ports darstellen. Wählen Sie dazu den Port aus, klicken Sie dann auf die rechte Maustaste und wählen Sie “Ungroup Selected Nodes”. Der Code aus den “with … select” Anweisungen wird als Multiplexer mit konstanten Dateneingängen dargestellt.

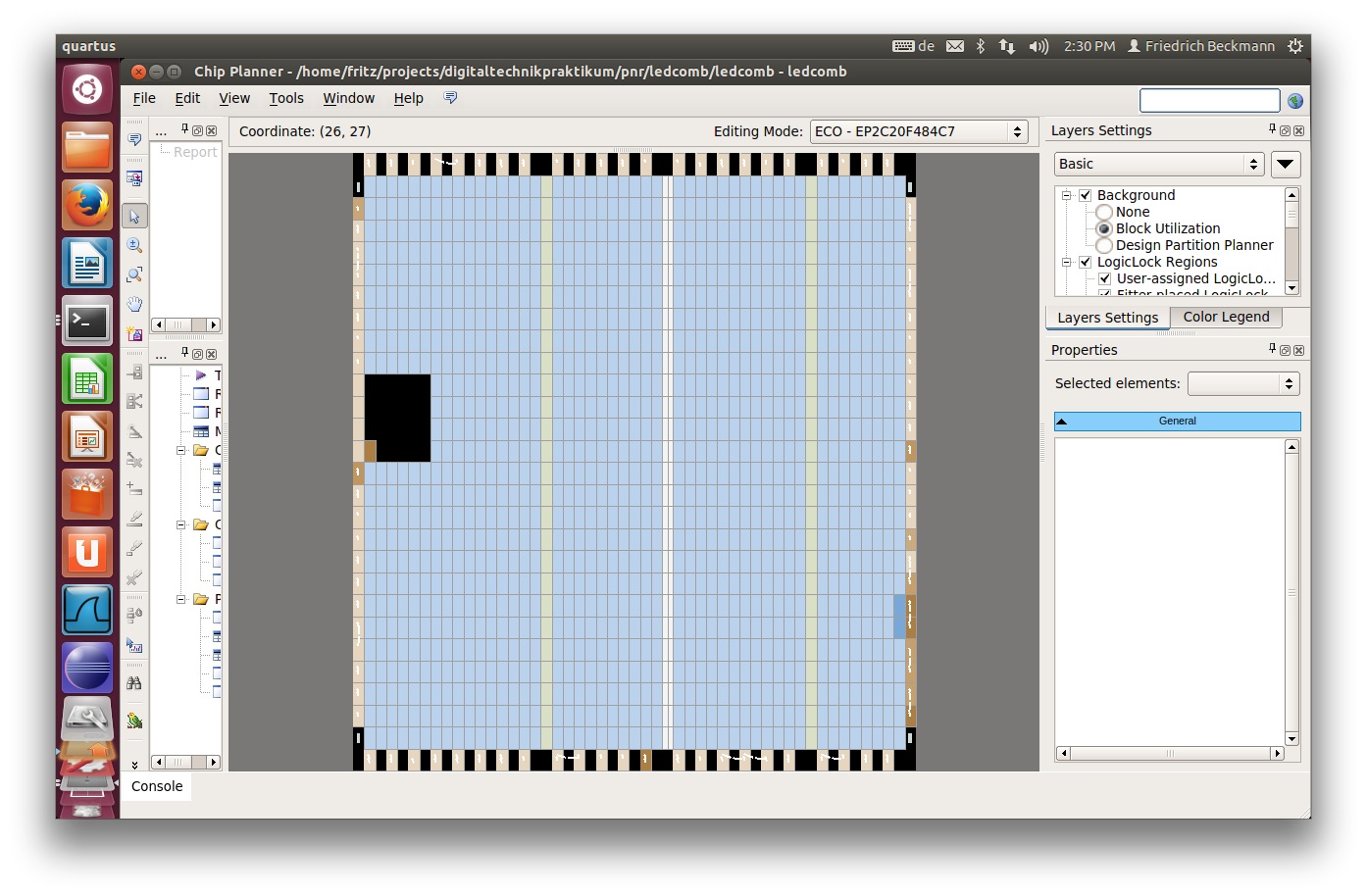

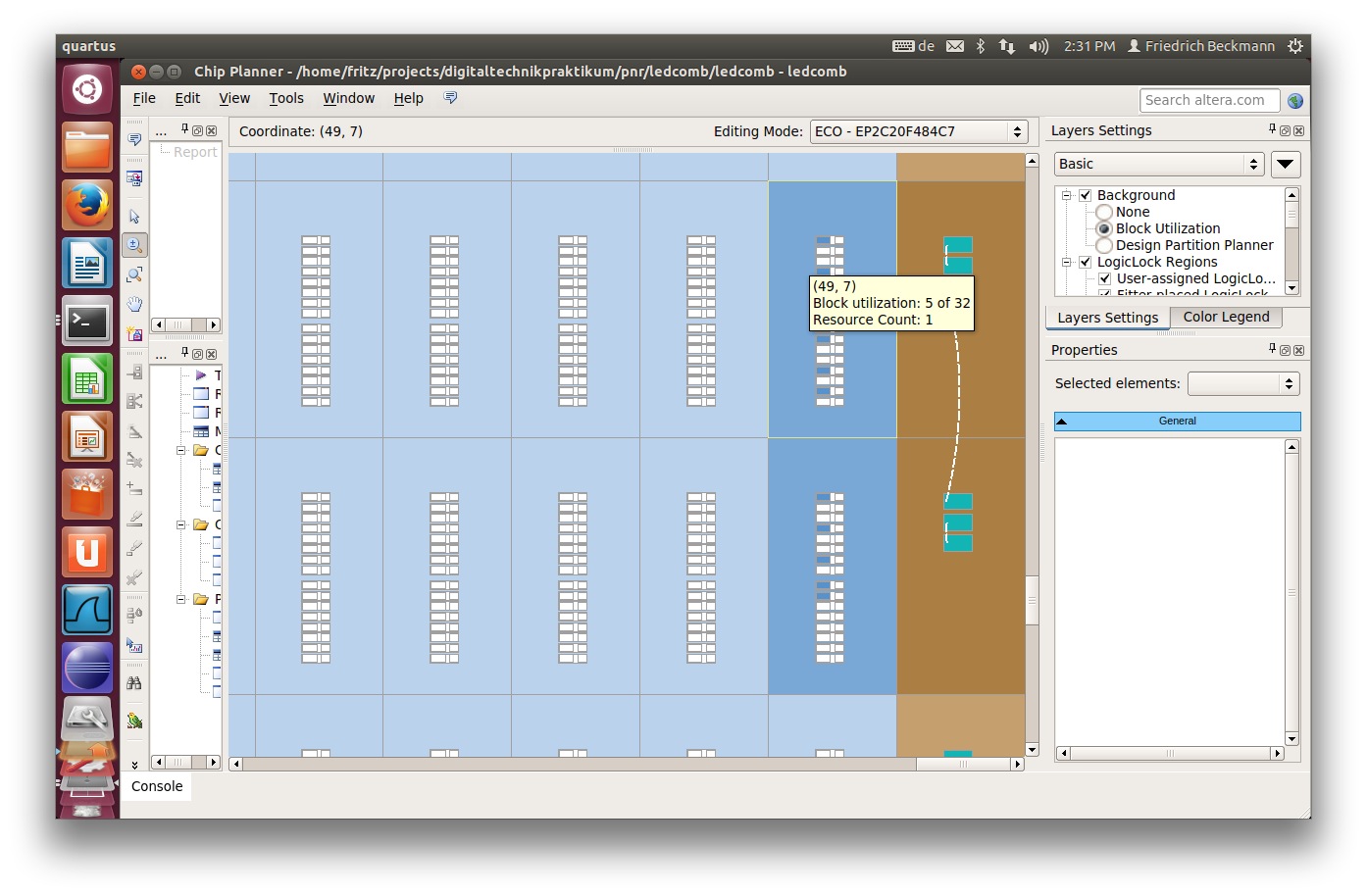

Starten Sie mit “Tools → Chip Planner” die Gesamtansicht des FPGA Chips.

Die hellblauen Felder sind die Felder mit leeren Logikelementen. Zoomen Sie in den Bereich mit den dunkelblauen Feldern. Die belegten Logikelemente sind blau markiert.

Mit einem Doppelklick auf ein Logikelement können Sie den Inhalt und die Belegung des Logikelementes darstellen.

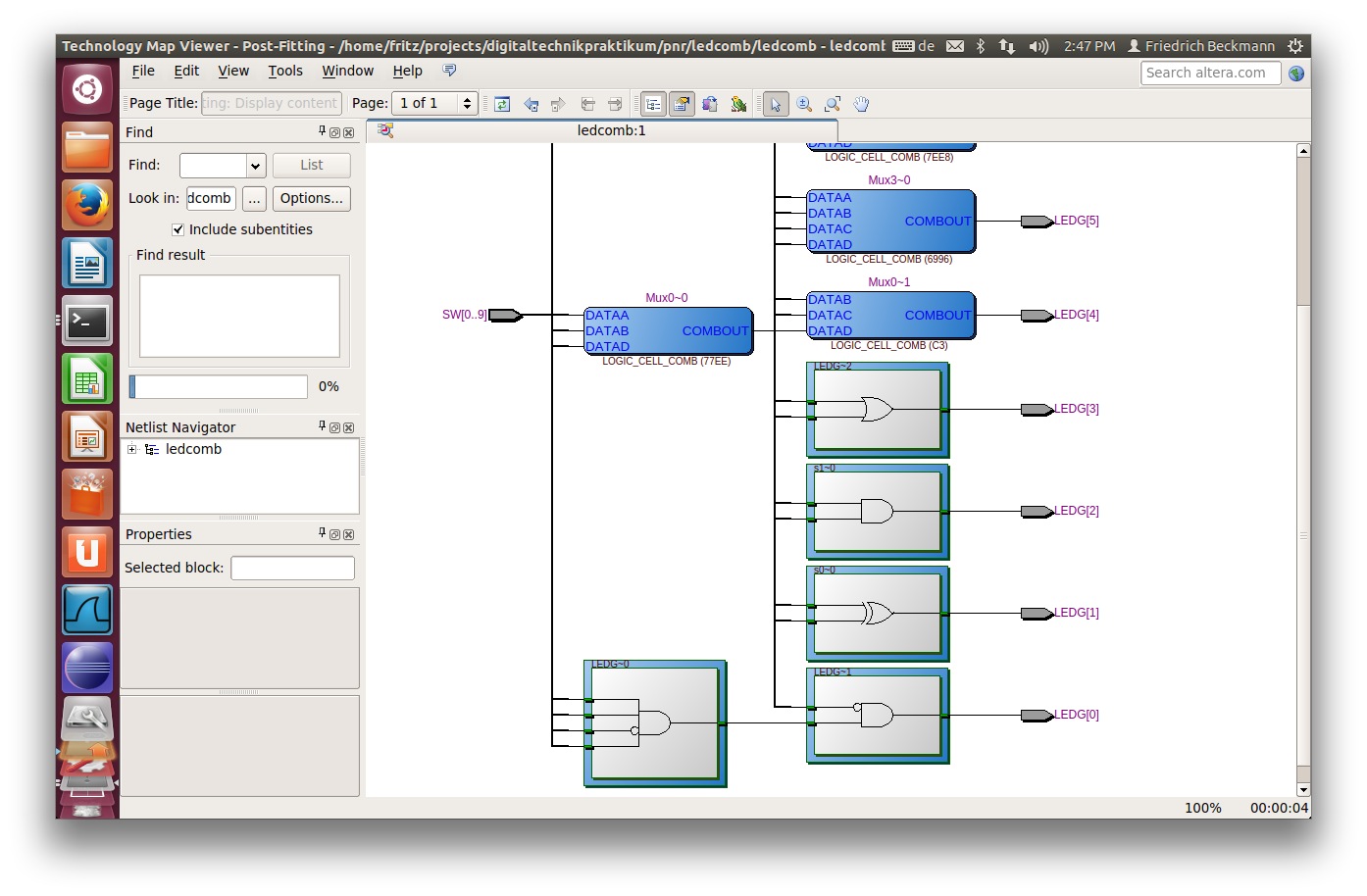

Starten Sie mit “Tools → Netlist Viewers → Technology Map Viewer (Post Fitting)” eine Schaltplananzeige mit der Verschaltung der einzelnen Logikelemente nach der Synthese.

Mit einem Doppelklick auf die Logikelemente wird die Konfiguration der Lookuptabelle als Schaltplan mit Logikgattern dargestellt.

- Weisen Sie nach, dass die Eingänge des Logikelementes, dessen Ausgang an LEDG(3) angeschlossen ist, die Eingänge SW(0) und SW(1) sind.

- Warum hat dieses Logikelement vor LEDG(3) eine ODER Funktion mit den Eingängen SW(0) und SW(1)?

- Warum wird die Funktion für LEDG(0) nicht mit einem, sondern mit zwei Logikelementen berechnet?

- Warum ist das Logikelement an LEDG(7) als UND Gatter konfiguriert?

Beispiel hierarchisches Design

In der Datei cntones_rtl.vhd finden Sie eine Schaltungsbeschreibung für eine Schaltung, die die Anzahl der Einsen an den vier Eingängen zählt.

Diese Einserzählschaltung soll jetzt genutzt werden um die Anzahl der Einsen an den SW(3..0) und SW(9..6) zu zählen. Das Ergebnis für SW(3..0) soll an LEDG(2..0) und für SW(9..6) an LEDG(7..5) dargestellt werden.

In der Datei de1_ledcntsw_rtl.vhd finden Sie die Schaltungsbeschreibung, die die Schaltung cntones zweimal instantiiert und mit den entsprechenden Eingängen und Ausgängen verbindet. Dazu gibt es das Syntheseverzeichnis “pnr/de1_ledcntsw”.

- An welcher Stelle ist festgelegt, dass jetzt die zwei VHDL Dateien de1_ledcntsw_rtl.vhd und cntones_rtl.vhd notwendig sind?

- Synthetisieren Sie die Schaltung.

- Stellen Sie mit dem RTL Viewer die Struktur der Schaltung dar.

- Überlegen Sie wieviele Logikelemente sie für die Schaltung verbrauchen und begründen Sie dies.

- Stellen Sie mit dem Technology Map Viewer das Ergebnis der Synthese dar und vergleichen Sie die Anzahl der benötigten Logikelemente mit Ihren Überlegungen.

Aufgabe Siebensegmentanzeige

Sie sollen eine Schaltung mit einer hierarchischen Schaltungsbeschreibung entwerfen, mit der die Schalter SW(3..0) als Binärdarstellung interpretiert als Hexadezimalzahl an HEX0 angezeigt wird. Weiterhin sollen die Schalter SW(9..6) als Hexdezimalzahl an HEX1 angezeigt werden.

- Erstellen Sie hierzu zunächst eine neue Datei bin2seg_rtl.vhd. Diese Schaltung bin2seg soll 4 Eingänge bin_i(3..0) und sieben Ausgänge seg_o(6..0) haben. Diese Schaltung berechnet die Übersetzung von Binärdarstellung in die Siebensegmentansteuerung.

In der Datei de1_bin2seg_rtl.vhd soll das Design de1_bin2seg auf Basis der bin2seg Schaltung enthalten sein. Dort werden die Schalter und HEX0 und HEX1 Anschlüsse vom FPGA Board mit der bin2seg Schaltung verbunden. Sie müssen dazu die Schaltung bin2seg mehrfach instantiieren - analog wie bei der cntsw Schaltung.

- Erstellen Sie die Datei de1_bin2seg_rtl.vhd

- Erstellen Sie ein Syntheseverzeichnis “pnr/de1_bin2seg” mit den zugehörigen Synthesedateien

- Synthetisieren Sie die Schaltung und laden Sie das Design auf das Board.

- Überprüfen Sie die gewünschte Funktion auf dem Board

Sie müssen hierfür einige VHDL Dateien und das Syntheseprojekt neu anlegen. In How to setup a new Module wird das Anlegen eines neuen Moduls Schritt für Schritt beschrieben.

Abgabe Versuchsbericht

Geben Sie einen Untersuchungsbericht zur “Siebensegmentanzeige” mit den Ergebnissen Ihrer Analysen als Bericht im Moodlekurs Digitaltechnik ab.

Abgabe Bericht zum Versuch "Kombinatorische Schaltungen"

Orientieren Sie sich inhaltlich an folgenden Punkten:

- Skizzieren Sie die Designhierarchie

- Kopieren Sie den von Ihnen geschriebenen VHDL Code in den Bericht und erläutern Sie die Funktion

- Zeigen Sie die Schaltung im RTL Viewer

- Dokumentieren Sie die Anzahl der benötigten Logikelemente für die Schaltung

- Dokumentieren Sie die Funktion der Schaltung auf dem Board

Bitte belegen Sie alle Aussagen im Bericht mit Nachweisen. Belegen Sie beispielsweise die Anzahl der benötigten Logikelemente für eine Schaltung mit einem geeigneten Screenshot von der Synthesesoftware.

Form

Alle Abbildungen im Bericht müssen fortlaufend numeriert und untertitelt sein. Tabellen müssen auch numeriert und mit einer Überschrift versehen sein. Für jede Abbildung und jede Tabelle muss im Text eine Erläuterung zu finden sein was in der Abbildung dargestellt ist. Ein Beispiel für die Form mit Titel, Abstract, Abbildung, Tabelle und Literaturverzeichnis ist die Maschine.