This is an old revision of the document!

Digitaltechnik Praktikum Versuch 1

Der erste Versuch dient als Einführung in die Modelsim Simulationssoftware und die Quartus Synthesesoftware. Als Beispiel dient Die erste Schaltung.

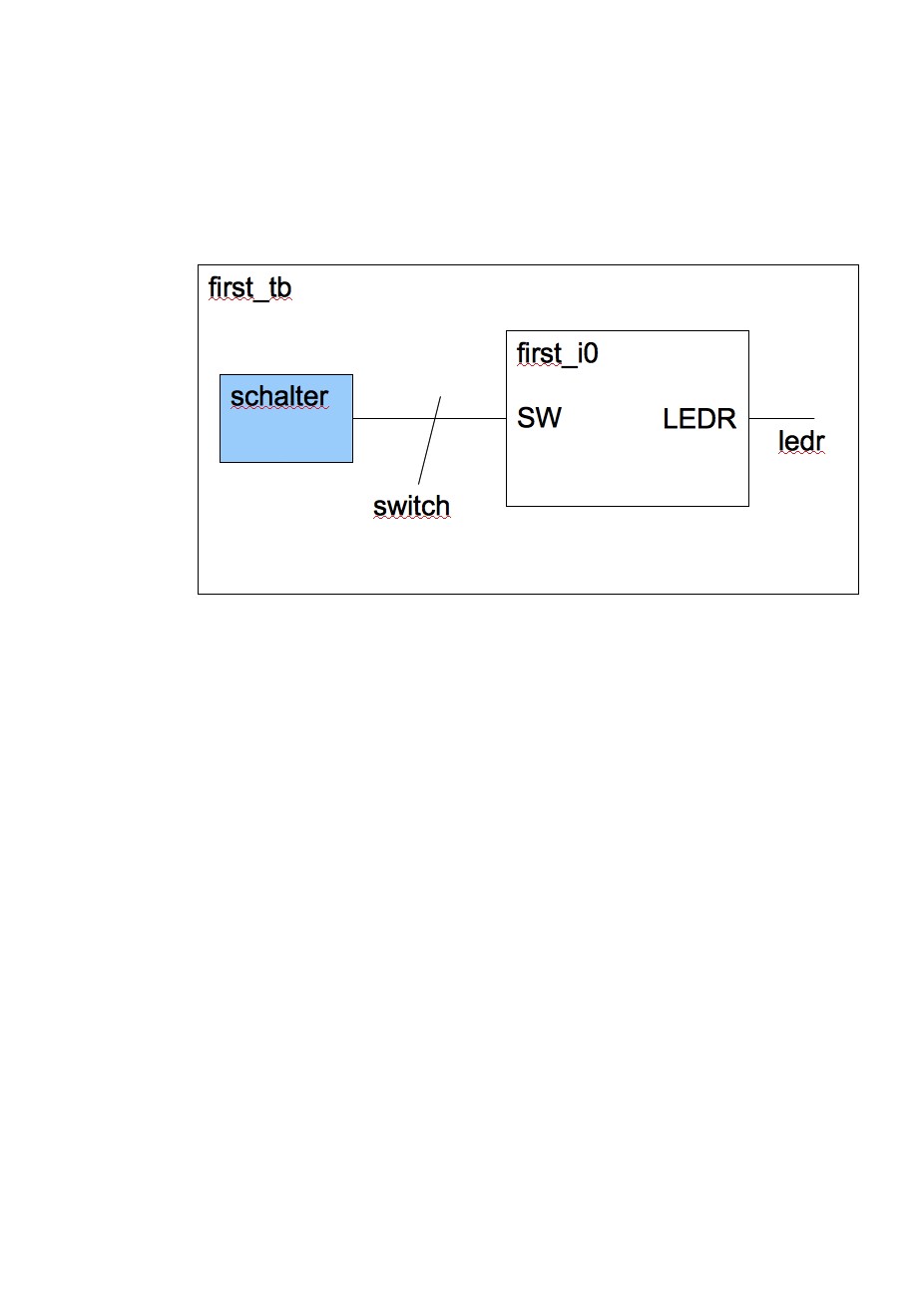

Die erste Schaltung hat den Namen first und besteht aus einer Testbench “first_tb” und der eigentlichen Schaltung “first”. Die Schaltung “first” ist in der Testbench “first_tb” instantiiert.

Die Anleitungen zur Simulation und Synthese:

Einführung in VHDL und Modelsim

Einführung in die Quartus Synthesesoftware

Für die Synthese ist die folgende Pinbelegungsdatei notwendig:

https://www.hs-augsburg.de/~beckmanf/restricted/DE1_pin_assignments.csv

Die Aufgaben

- Simulieren Sie die Schaltung “first” gemäß der Einführung in VHDL und Modelsim

- Erzeugen Sie eine Belegungsdatei für das FPGA Board gemäß der Einführung in die Quartus Synthesesoftware

- Programmieren Sie das FPGA Board und prüfen Sie dort die Funktion

- Bitten Sie Ihren Betreuer einen Fehler in den Code einzubauen. Korrigieren Sie dann den Fehler.

- Erweitern Sie die Testbench und testen Sie weitere Eingangskombinationen

- Ändern Sie die Schaltung und schalten Sie mit Schalter 0-4 gleichzeitig LED 0-4 und LED 5-9 ein. Also Schalter 0 schaltet gleichzeitig LED 0 und LED 5 ein oder aus. Tip: Um einen Teil eines Busses auszuwählen, können Sie den Teilbereich mit dieser Syntax auswählen: sw[4 downto 0]. Tip 2: Um zwei Busse zu einem Bus zusammenzufassen, kann man die Busse mit dem & Zeichen aneinanderhängen. Beispiel: busa[4 downto 0] ⇐ busb[2 downto 0] & busc[9 downto 8] bedeutet: Den Bussignalen 4,3,2 von busa, werden die Signale 2,1,0 von busb zugewiesen und den Signalen 1,0 von busa werden die Signale 9 und 8 von busc zugewiesen.

- Simulieren Sie die neue Schaltung

- Prüfen Sie die Funktion auf dem FPGA