Digitaltechnikpraktikum Versuch 3 - Arithmetische Schaltung

In diesem Versuch

- analysieren Sie die Schaltung zur Addition von Binärzahlen

- entwerfen Sie eine Schaltung mit dem das Additionsergebnis auf dem FPGA angezeigt wird

- entwerfen Sie die Abstimmungsschaltung für 10 Schalter

- messen Sie die Verzögerungszeit der Abstimmungsschaltung

Projektaktualisierung

Aktualisieren Sie ihr Projekt mit “git pull”.

Additionsschaltung mit VHDL

In der Datei add4_rtl.vhd ist eine Schaltung zur Addition von zwei 4 Bit Binärzahlen mit einem 4 Bit Ergebnis in VHDL beschrieben.

Sie verwenden diese Schaltung um auf dem FPGA zwei Zahlen zu addieren. Die beiden Summanden sollen an den Schaltern SW(3..0) und SW(9..6) als Binärzahl vorliegen. Der Zustand der Schalter soll an den roten LEDs angezeigt werden. Gleichzeitig soll ein Summand an HEX0 und der andere Summand an HEX1 als Ziffer dargestellt werden. Das Ergebnis der Addition soll an den grünen LEDs LEDG(3..0) binär und an HEX2 als Ziffer dargestellt werden. Diese Schaltung soll den Namen de1_add4 haben. Es ist auch schon eine unvollständige VHDL Datei de1_add4_rtl.vhd vorhanden, die Sie noch ergänzen müssen. Das Syntheseverzeichnis pnr/de1_add4 ist schon fertig vorbereitet.

- Wechseln Sie in das Syntheseverzeichnis pnr/de1_add4 und starten Sie Quartus mit der grafischen Oberfläche.

- Ergänzen Sie den VHDL Code in der Datei de1_add4_rtl.vhd

- Laden Sie das Design auf das FPGA und überprüfen Sie dort die Funktion

Analyse der Additionsschaltung

Jetzt geht es um die Analyse wie die Additonsschaltung intern auf dem FPGA mit den Logikelementen umgesetzt wird. Im Cyclone II Datenblatt ist auf Figure 2-3 die Konfiguration des Logikelementes im “Normal Mode” und in Figure 2-4 im “Arithmetic Mode” dargestellt. Der Eingang “cin” des Logikelementes ist immer mit dem “cout” Ausgang des direkt benachbarten Logikelementes verbunden. Im “Arithmetic Mode” ist die Lookuptabelle in zwei 3→1 Lookuptabellen aufgeteilt, wobei der Ausgang der einen Lookuptabelle immer “cout” ist und deshalb nur zum Nachbarlogikelement weitergegeben werden kann.

- Starten Sie quartus mit der GUI im Syntheseverzeichnis “pnr/de1_add4”

- Öffnen Sie den RTL Viewer und analysieren Sie die Schaltungsstruktur auf VHDL Ebene

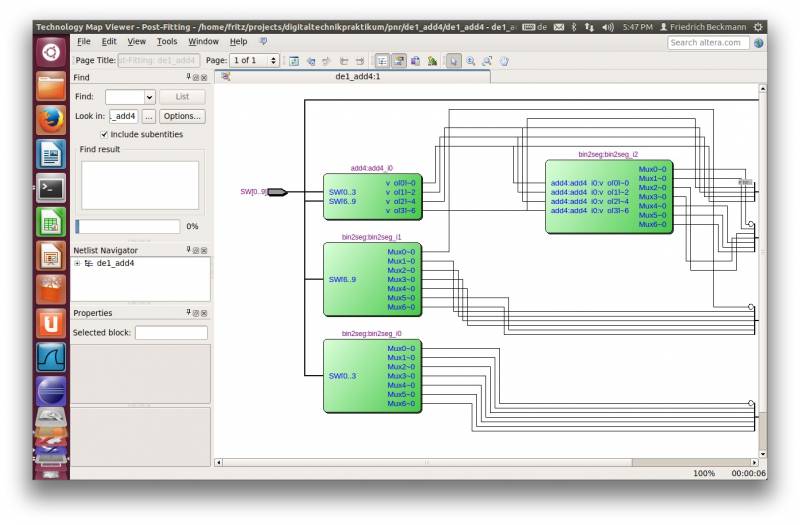

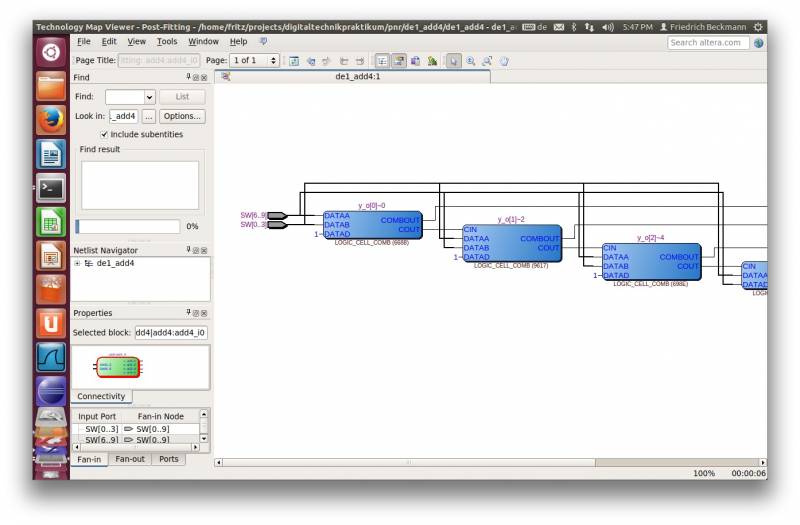

- Öffnen Sie den Technology Map Viewer (Post Fitting) und analysieren Sie die Schaltungsstruktur

Öffnen Sie das Design “add4” im Technologymap Viewer

Skizzieren Sie die Verschaltung der Logikelemente untereinander auf Papier.

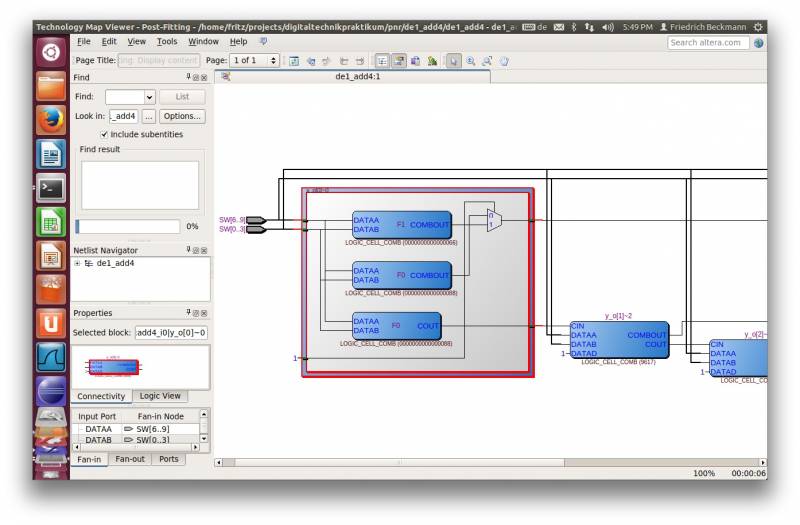

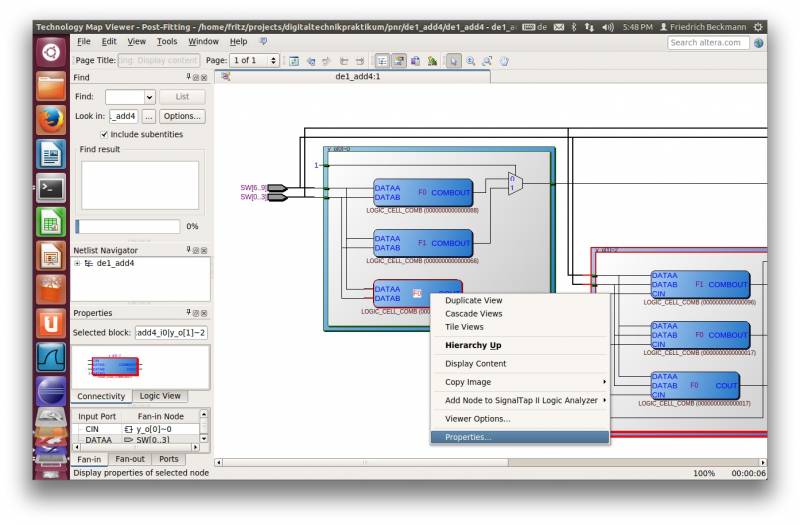

Stellen Sie den Inhalt der einzelnen Logikelement durch Doppelklicken auf das Logikelement dar.

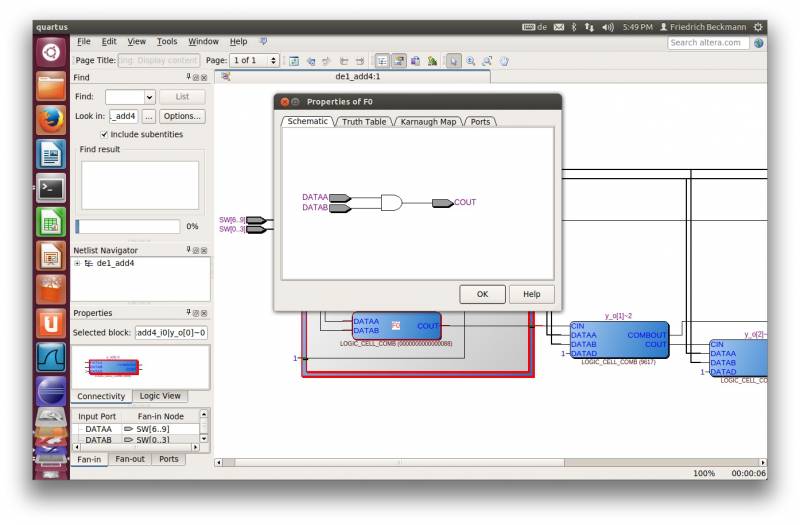

Der Multiplexer in dem Logikelement hat einen konstanten Selecteingang. Welche Lookuptabelle ist deshalb am Ausgang des Multiplexers wirksam? Die Eigenschaften der beiden Lookuptabellen F0 und F1 innerhalb des Logikelementes können Sie sich nach Auswahl der Lookuptabelle und Klick auf die rechte Maustaste im Kontextmenü “Properties” anschauen.

Danach erscheint ein Fenster mit der Darstellung der booleschen Funktion in der Lookuptabelle.

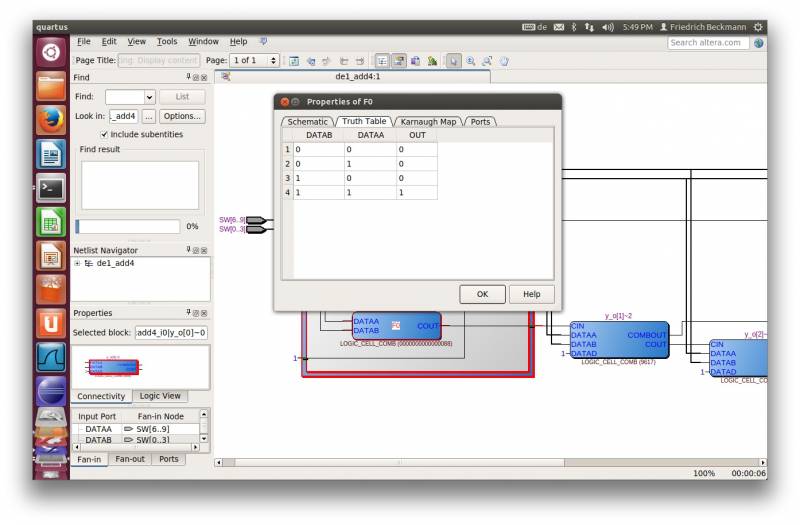

Dort kann dann die Darstellung als Wahrheitstabelle “Truth Table” gewählt werden.

- Welche Logikelemente sind im “Normal Mode”, welche sind im “Arithmetic Mode”?

- Vergleichen Sie die Schaltung mit dem “Ripple-Carry-Addierer” in Kapitel 10.8.2 im "Lehrbuch Digitaltechnik" von Reichardt.

- Analysieren Sie die booleschen Funktionen der einzelnen Lookuptabellen in den Logikelementen und notieren Sie die Wahrheitstabellen auf Papier.

- Vergleichen Sie die Funktionen mit der Funktion eines Halb- und eines Volladdierers.

- Welche Unterschiede gibt es in dieser Schaltung im Vergleich zum Ripple-Carry-Addierer?

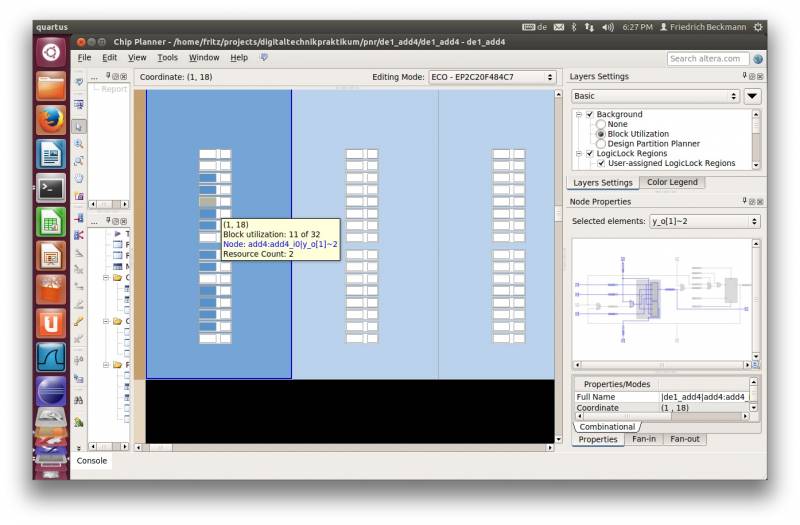

Öffnen Sie jetzt den Chip Planner und suchen Sie die Logikelemente, die zum Addierer gehören. Die Logikelemente haben im Namen irgendetwas mit “add”.

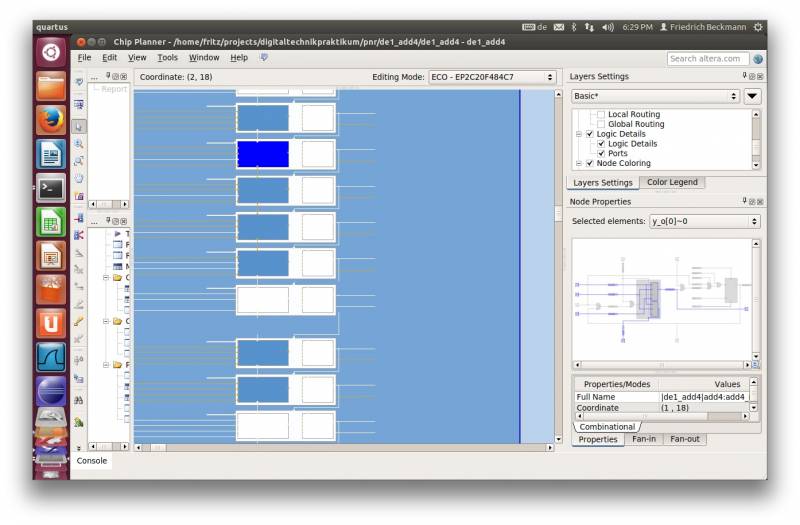

- Aktivieren Sie mit “View → Layers Settings” die Auswahl für die Darstellung

- Aktivieren Sie Logic Details → Ports

- Finden Sie die Verbindungungen zwischen “cin” und “cout” zwischen den Logikelementen vom Addierer.

Entwurf der Abstimmungsschaltung

Sie haben bislang folgende Schaltungen in Ihrem Baukasten

- “add4”: Ein 4 Bit Addierer

- “bin2seg”: Eine Schaltung zur Anzeige einer 4 Bit Binärzahl an einer Siebensegmentanzeige

- “cntones”: Eine Schaltung zum Zählen von der Einsen an vier Eingängen.

- Allgemeine boolesche Ausdrücke und Wahrheitstabellen

Entwerfen Sie jetzt eine Abstimmungsschaltung mit zehn Eingängen. In der Vorlesung haben Sie eine Abstimmungsschaltung mit drei Eingängen durch Nachdenken und direkt aus einer Wahrheitstabelle entworfen. Entwerfen Sie jetzt auf Papier eine Schaltung auf Basis der oben genannten Komponenten! Die Schaltung soll folgende Eigenschaften haben

- LEDG(7) soll leuchten, wenn mehr als fünf Schalter SW(9..0) eingeschaltet sind

- Der Zustand der Schalter SW(9..0) soll an LEDR angezeigt werden.

- Verwenden Sie die HEX Anzeigen für die Darstellung von internen Werten nach Belieben.

Wenn Sie die Schaltung auf Papier skizziert haben, dann können Sie sich an die Umsetzung in VHDL machen. Für die Abstimmungsschaltung gibt es eine Testbench t_de1_majority.vhd und eine angefangene Datei de1_majority.vhd für das Design. Das Simulationsverzeichnis sim/de1_majority und das Syntheseverzeichnis pnr/de1_majority sind fertig.

Für die Umsetzung in VHDL ist es eventuell notwendig, dass Sie mit Signalvektoren unterschiedlicher Länge arbeiten müssen. Dafür gibt es hier noch einige Tips. Sie haben bereits auf Teile aus einem Vektor zugegriffen, z.B. mit SW(3 downto 0) um einen vier Bit langen Vektor zu erhalten. Der Eingang switches_i der cntones Schaltung hat eine Länge von vier Bit. Wenn Sie die Eingänge switches_i(1 downto 0) mit SW(5 downto 4) verbinden wollen und switches_i(3 downto 2) auf 0 setzen wollen geht das so:

cntones_i0 : cntones port map ( switches_i(1 downto 0) => SW(5 downto 4), switches_i(3 downto 2) => "00", cnt_o => cnt);

Wenn Sie nur den einen Eingang switches_i(3) auf 0 setzen wollen und switches_i(2 downto 0) mit den Schaltern SW(2 downto 0) verbinden wollen, dann geht das so:

cntones_i0 : cntones port map ( switches_i(2 downto 0) => SW(2 downto 0), switches_i(3) => '0', cnt_o => cnt);

- Entwerfen Sie die Abstimmungsschaltung auf Papier

- Entwerfen Sie die Abstimmungsschaltung in VHDL

- Simulieren Sie die Schaltung im Verzeichnis sim/de1_majority

- Sorgen Sie dafür, dass kein Ausgang bei der Simulation “undefined” ist

- Wenn die Schaltung funktioniert, starten Sie die Synthese im Verzeichnis pnr/de_majority

- Überprüfen Sie die Funktion auf dem FPGA.

Messung der Verzögerungszeit der Schaltung

Jetzt messen Sie die Verzögerungszeit der Schaltung auf dem FPGA. Dazu verwenden Sie den Expansionport “GPIO_1”. Für diese Messung soll nicht der Signalgenerator verwendet werden, sondern der 50 MHz Oszillator, der schon auf dem Board vorhanden ist. Um das 50 MHz Signal vom Oszillator auch messen zu können, wird es erst durch das FPGA auf den Expansionport geführt und dann vom Expansionport wieder zurück in den FPGA an die Schaltung.

- Überlegen Sie von welchem Schalter aus es die größte Verzögerungszeit zum Ausgang der Abstimmungsschaltung geben könnte.

- Fügen Sie einen Eingang CLOCK_50 zum Design hinzu

- Fügen Sie einen Ausgang CLOCK_50_OUT zum Design hinzu

- Fügen Sie einen Eingang CLK_IN zum Design hinzu

- Fügen Sie einen Ausgang MAJ zum Design hinzu

- Ersetzen Sie den Schaltereingang, der wahrscheinlich der Startpunkt der längsten Verzögerung ist, durch den Eingang CLK_IN

- Verbinden Sie neben LEDG(7) auch den Ausgang MAJ mit dem Ausgang der Abstimmungsschaltung

- Leiten Sie auf dem FPGA das 50 MHz Taktsignal, das am Eingang CLOCK_50 ankommt, zum Ausgang CLOCK_50_OUT.

Jetzt müssen Sie noch geeignete Pindefinitionen zum Pindefinitionsfile hinzufügen um

- CLOCK_50 mit dem 50 MHz Oszillator

- CLOCK_50_OUT mit dem Pin 1 auf dem Expansionport 1 (GPIO1)

- CLK_IN mit dem Pin 2 auf Expansionport 1

- MAJ mit dem Pin 40 auf dem Expansionport 1

zu verbinden.

Nach etwas Recherche im Altera DE1 Usermanual sollte dabei herauskommen:

set_location_assignment PIN_L1 -to CLOCK_50 set_location_assignment PIN_H12 -to CLOCK_50_OUT set_location_assignment PIN_H13 -to CLK_IN set_location_assignment PIN_P18 -to MAJ

- Messen Sie die Verzögerungszeit durch das FPGA!