Digitaltechnik Praktikum Versuch 6 - VGA Signal

In diesem ersten Versuch geht es um die Analyse des VGA Signals mit dem Logikanalysator und den Entwurf einer Schaltung zur Erzeugung des horizontalen Synchronisationssignals.

Vorbereitung

Zur Vorbereitung des Versuchs müssen Sie sich in die Funktion der VGA Schnittstelle vertraut machen. Die folgenden Links beschreiben die Funktionsweise der VGA Schnittstelle.

http://en.wikipedia.org/wiki/Video_Graphics_Array

http://lslwww.epfl.ch/pages/teaching/cours_lsl/ca_es/VGA.pdf

http://www.tinyvga.com/vga-timing/640x480@60Hz

Im DE1 Usermanual

ist die Verschaltung des VGA Anschlusses FPGA in Kapitel 4.6 dargestellt.

In der praktischen Prüfung müssen Sie einen Bericht über Ihren Entwurf, die Simulationen und die Messungen abgeben. Deshalb haben Sie hier die Gelegenheit solche Berichte abzugeben. Die Form des Berichts ist hier: Form der Berichts beschrieben.

Fragen zur Vorbereitung

- Wozu dient ein VGA Anschluss? Was kann man an einen VGA Anschluss anschliessen?

- Was wird über die drei Anschlüsse R, G und B über den VGA Anschluss übertragen?

- Wie schnell können sich die Signale an R, G und B bei einer Videoauflösung von 640×480 ändern?

- Was sind die minimale und die maximale Spannung der R, G und B Signale?

- Was bedeutet Pixeltakt? Welche Frequenz hat der Pixeltakt bei einer Auflösung von 640×480 Punkten?

- Was passiert in einem Röhrenmonitor wenn das HSYNC Signal aktiv ist?

- Was passiert in einem Röhrenmonitor wenn das VSYNC Signal aktiv ist?

- Ist die Frequenz des HSYNC Signals größer oder kleiner als die des VSYNC Signals?

- Was ist die front porch und die back porch time?

- Ist die front porch time für das VSYNC Signal länger oder kürzer als die front porch time für das HSYNC Signal?

- Warum kann man die Länge des HSYNC Signals in Pixeln und die Länge des VSYNC Signals in Zeilen angeben?

- Was ist die typische Leitungsimpedanz eines VGA Kabels?

- Welche Spannung stellt sich am VGA Steckerpin R ein, wenn VGA_R0 bis VGA_R2 auf “L” und VGA_R3 auf “H” liegen? Die Namen beziehen sich auf Figure 4.11 im DE1 Usermanual.

- Welche Farbe wird ein Pixel haben, wenn alle Signale VGA_R(3..0), VGA_G(3..0), VGA_B(3..0) auf “L” liegen?

- Welche Farbe wird ein Pixel haben, wenn alle Signale VGA_R(3..0), VGA_G(3..0), VGA_B(3..0) auf “H” liegen?

Laboraufgaben

Installieren Sie das Projektverzeichnis mit

git clone https://gitlab.elektrotechnik.hs-augsburg.de/beckmanf/eds1.git

Analyse des VGA DAC

Auf dem DE1 Board befindet sich der VGA Digital-Analog Wandler (DAC). Der Schaltplan des DE1 Boards ist hier:

https://www.hs-augsburg.de/~beckmanf/restricted/DE1_V.1.0.1_CDROM/DE1_schematics/de1_v11a.pdf

Bei dem DAC soll die statische Übertragunskennlinie analytisch und experimentell untersucht werden. Die Ergebnisse werden mit einer idealen Kennlinie verglichen. Für alle Untersuchungen sind handschriftliche Aufzeichnungen notwendig.

- Es werden vier Teams aus den Laborgruppen gebildet. Zwei Teams untersuchen den DAC analytisch und zwei Teams experimentell. Jedes Team hat maximal vier Mitglieder.

- Die (2er) Gruppen in den Teams arbeiten zunächst unabhängig voneinander und notieren die Ergebnisse auf einem Zettel.

- Die 2er Gruppen vergleichen dann die Ergebnisse mit den Ergebnissen der anderen Gruppe im Team.

- Jedes Team entwirft ein Flipchart mit den Ergebnissen. Jedes Teammitglied muss die Ergebnisse erläutern können. So entstehen insgesamt vier Flipcharts.

- Jedes Team teilt sich auf. Die eine Hälfte des Teams bleibt bei dem eigenen Flipchart um Fragen zu beantworten (Erklärer). Die andere Hälfte (Wanderer) besucht reihum die anderen Flipcharts. Beim Zeitzeichen geht jede Wandergruppe eine Station weiter.

- Danach tauschen die Wanderer und die Erklärer ihre Rollen.

Analytische Untersuchung des DAC

- Finden Sie im DE1 Schaltplan den DAC.

- Zeichnen Sie ein Ersatzschaltbild eines Farbkanals des DAC. Fassen Sie Reihen- und Parallelschaltungen von Widerständen zusammen. Wie modellieren Sie die digitalen Ausgänge des FPGA?

- Erklären Sie die Funktion des DAC.

- Finden Sie einen analytischen Ausdruck für die Ausgangsspannung eines Farbkanals in Abhängigkeit vom digitalen Zustand der Ausgänge.

- Starten Sie eine Tabellenkalkulation und berechnen Sie die Ausgangsspannung für jeden digitalen Wert.

- Vergleichen Sie die berechneten Werte mit der idealen Kurve.

- Welche Unterschiede gibt es?

- Wie hängt die Linearität vom Lastwiderstand ab?

Experimentelle Untersuchung

- Entwerfen Sie auf dem Papier eine Schaltung mit der Sie die Ausgangsspannung am roten Farbkanal messen können. Aus dem Schaltplan soll ersichtlich sein, welche Komponenten des DE1 Boards sie verwenden und wo Sie messen wollen.

- Zeichnen Sie ein Ersatzschaltbild des VGA_R Farbkanals des DAC. Fassen Sie Reihen- und Parallelschaltungen von Widerständen zusammen. Wie modellieren Sie die digitalen Ausgänge des FPGA?

- Berechnen Sie die erwarteten Spannungen für VGA_R(3..0) = “0000” und “1111”.

- Erstellen Sie eine Schaltung de1_vgadac mit der zu erstellenden VHDL Datei “de1_vgadac_rtl.vhd” mit der Sie den roten VGA Kanal über die Schalter SW3 bis SW0 kontrollieren können. Das zugehörige pnr Verzeichnis soll de1_vgadac heissen.

- Wie können Sie mit dieser Schaltung die Kennlinie messen?

- Messen Sie die Ausgangsspannungen für alle möglichen Wertekombinatonen von VGA_R.

- Berechnen Sie die Werte bei idealem DAC Verhalten.

- Vergleichen Sie das gemessene Verhalten mit dem idealen Verhalten.

Messung und Analyse eines unbekannten VGA Signals

Messung und Analyse in der Gruppe

Zunächst sollen die Signalverläufe eines unbekannten VGA Signals am Ausgang des DE1 FPGA Boards gemessen und analysiert werden. In dieser vga-messungen-fpga-belegung.zip Datei ist für jede Gruppe eine FPGA Belegungsdatei enthalten. Laden Sie die FPGA Belegungsdatei für Ihre Gruppe über den Quartus Programmer auf das FPGA. Ihre Aufgabe ist die Messung und Analyse des Signals mit dem Oszilloskop und dem Logikanalysator. Im Rahmen eines schriftlichen Analyseberichts müssen Sie folgende Fragen beantworten.

- Welche Polarität hat das VSYNC Signal? Ist es high- oder low-aktiv?

- Welche Polarität hat das HSYNC Signal? Ist es high- oder low-aktiv?

- Für welchen Zeitraum ist das VSYNC Signal aktiv?

- Für welchen Zeitraum ist das HSYNC Signal aktiv?

- Mit welcher Frequenz wiederholt sich das VSYNC Signal?

- Mit welcher Frequenz wiederholt sich das HSYNC Signal?

- Wie ist die Bildwiederholfrequenz?

- Wie viele Zeilen hat das VGA Signal pro Bild? Warum?

- Welche Auflösung hat das Bild?

- Geben Sie die front porch und back porch Zeit für das HSYNC Signal an.

- Geben Sie die front porch und back porch Zeit für das VSYNC Signal an.

- Skizzieren Sie den Amplitudenverlauf für die R, G und B Signale.

- Skizzieren Sie das Bild, das am Monitor erscheint, wenn Sie das FPGA an einen Monitor anschliessen. Geben Sie die Farben im Bild an.

Begründen Sie Ihre Antworten und nehmen Sie Messbilder vom Oszilloskop in Ihren Bericht mit auf. Zu der Antwort müssen geeignete Messungen (mit Bild) im Bericht vorhanden sein.

Bericht

Sie können den Bericht mit Libreoffice auf den Laborrechnern schreiben. Vom Laborrechner können Sie auch auf dem Labordrucker drucken. Laden Sie die Oszilloskopbilder über das Webinterface vom Oszilloskop und verwenden Sie Bilder ohne schwarzen Hintergrund. Die IP Adresse vom Oszilloskop können Sie am Oszilloskop über Tools→Utility→I/O erfahren. Wenn Sie alle Fragen in Ihrem Bericht beantwortet haben, legen Sie den Bericht einem Betreuer vor, der den Bericht mit Ihnen durchgehen wird.

Laden Sie den Bericht als pdf Datei mit dem Dateinamen “eds1_vgadac_<name1>_<name2>.pdf” im Moodlekurs hoch.

Anschluss eines VGA Monitors an das Board

Wenn Sie mit Ihrer Ausarbeitung fertig sind und ein Betreuer den Bericht abgenommen hat, wird der VGA Monitor an das FPGA angeschlossen und das erwartete Bild mit dem Monitorbild verglichen.

Zulässige Komponenten für den Schaltungsentwurf

In den weiteren Versuchen werden Sie auf dem Papier Schaltungen entwerfen. Für den Schaltungsentwurf sollen Sie die folgenden Grundkomponenten nach Bedarf verwenden.

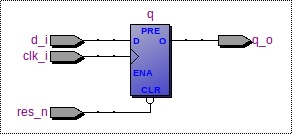

D-Flipflop

Ein einfaches D Flipflop mit positiver Flankensteuerung und low aktivem Reset.

Das Flipflop kann mit folgendem VHDL Code erzeugt werden:

entity ff is port( clk_i, res_n : in std_ulogic; d_i : in std_ulogic; q_o : out std_ulogic); end; architecture rtl of ff is begin q_o <= '0' when res_n = '0' else d_i when rising_edge(clk_i); end architecture;

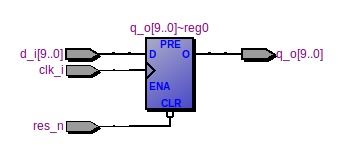

Register

Ein Register mit einstellbarer Bitbreite.

entity reg is port( clk_i, res_n : in std_ulogic; d_i : in std_ulogic_vector(9 downto 0); q_o : out std_ulogic_vector(9 downto 0)); end; architecture rtl of reg is begin q_o <= "0000000000" when res_n = '0' else d_i when rising_edge(clk_i); end architecture;

Im folgenden Beispiel wird das Register direkt auf Basis von Signalen erzeugt:

architecture rtl of example is signal d, q : std_ulogic_vector(9 downto 0); signal clk, res_n : std_ulogic; begin q <= "0000000000" when res_n = '0' else d when rising_edge(clk); -- weiterer Code -- end architecture rtl;

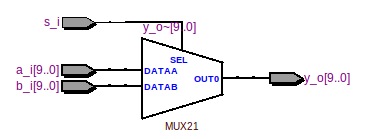

Multiplexer

Ein Multiplexer mit einstellbarer Bitbreite

Hier ein Codebeispiel für einen 2 zu 1 Multiplexer

entity mux is port( a_i,b_i : in std_ulogic_vector(9 downto 0); sel_i : in std_ulogic; y_o : out std_ulogic_vector(9 downto 0)); end; architecture rtl of mux is begin y <= a_i when sel_i = '0' else b_i; end architecture;

Und hier ein Beispiel für einen 4 zu 1 Multiplexer mit Signalen

architecture rtl of example is signal a,b,c,d,y : std_ulogic_vector(9 downto 0); signal sel : std_ulogic_vector(1 downto 0); begin with sel select y <= a when "00", b when "01", c when "10", d when others; -- weiterer Code end architecture;

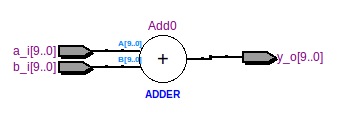

Addierer

Ein Addierer mit einstellbarer Bitbreite

Der Addierer steht als VHDL Komponente in src/adder_rtl.vhd zur Verfügung.

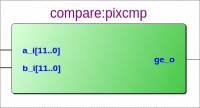

Vergleicher

Ein Vergleicher mit ge_o = '1', wenn a >= b, sonst '0'.

Der Vergleicher steht als VHDL Komponente in src/compare_rtl.vhd zur Verfügung.

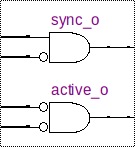

Logik auf Basis von booleschen Ausdrücken

Logik als Resultat von beliebigen booleschen Ausdrücken in VHDL.

-- Beispiel sync_o <= a and not(b); active_o <= not(a) and not(b); y_o <= not(a and not(b)) xor c;

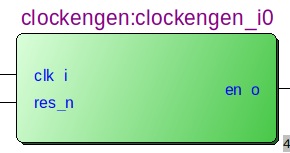

Design Clock Enable Generator

Entwerfen Sie jetzt einen Generator, der ein Enablesignal für jeden zweiten Takt generiert. Ein Zähler mit Enableeingang, der mit 50 MHz Taktfrequenz getaktet ist, würde mit diesem Enablesignal mit 25 MHz hochzählen.

Der Generator soll die Ein- und Ausgänge gemäß des vorherigen Bildes haben.

Zusammenarbeit

Bei dieser Aufgabe sollen alle Kursteilnehmer möglichst schnell zu einem funktionierenden Entwurf und dann zu einer funktionierenden Implementierung kommen.

Entwurfsphase

In der Entwurfsphase soll auf dem Papier der Entwurf des Enablegenerators erfolgen. Zeichnen Sie einen Schaltplan, benennen Sie Signale und zeichnen Sie geeignete Timingdiagramme auf denen die Signalverläufe der Ein- und Ausgänge zu sehen sind.

- Zeichnen Sie ein Timingdiagramm mit dem gewünschten Signalverlauf.

- Machen Sie einen Entwurf und zeichnen Sie einen Schaltplan. Benennen Sie Ein- und Ausgänge sowie interne Signale.

- Machen Sie sich Gedanken was Sie benötigen um Ihren Entwurf einer anderen Gruppe zu erklären.

Unabhängig von dem Entwurf bisher sollen Sie auch einen Entwurf auf Basis eines Mooreautomaten machen.

- Geben Sie die Ein- und Ausgänge des Automaten an.

- Benennen Sie die notwendigen Zustände

- Zeichnen Sie den Zustandsgraphen

- Zeichnen Sie ein Timingdiagramm mit Takt, Zustand und Ausgang des Automaten.

- Geben Sie eine Zustandskodierung an und geben Sie die Zustandsübergangslogik und die Ausgangslogik an.

Erklärungsphase

Jeweils zwei Gruppen erklären sich gegenseitig den Entwurf.

- Eine Gruppe erklärt einer anderen Gruppe den Entwurf (3 min).

- Danach können Fragen gestellt und der Entwurf diskutiert werden. Notieren Sie Änderungen.

- Danach wechseln die Rollen.

Designphase und Verifikation

In der Designphase soll der Entwurf in VHDL umgesetzt und verifiziert werden. Sie müssen dazu ein neues Designmodul anlegen. In How to setup a new Module wird dies beschrieben.

- Setzen Sie jetzt Ihr clockengen Design in VHDL um. Legen Sie dazu die VHDL Datei “clockengen_rtl.vhd” an. Verwenden Sie Signalnamen aus Ihrem Papierentwurf.

- Verifizieren Sie Ihr Design im Simulator. Das Simulationsverzeichnis soll “clockengen” heissen. Der Dateiname der Testbench soll “t_clockengen.vhd” lauten.

- Jetzt soll der Clock Enable Generator auf dem FPGA Board verifiziert werden. Zeigen Sie die Signalverläufe auf dem Oszilloskop. Instantiieren Sie das clockengen Design dazu in einem toplevel Modul, das de1_clockengen heissen soll. Die Ports in de1_clockengen sollen die Pins auf dem FPGA repräsentieren. Der Name der vhdl Datei vom Toplevel soll “de1_clockengen_rtl.vhd” sein.

- Dokumentieren Sie das Design, die Simulationsergebnisse und die Messergebnisse in einem Bericht mit dem Dateinamen “eds1_clockengen_<name1>_<name2>.pdf” und laden Sie den Bericht im Moodlekurs hoch.